# El Microcontrolador ATMega328P de Microchip:

Programación en Ensamblador, Lenguaje C y un enlace con Arduino

Felipe Santiago Espinosa

## El Microcontrolador ATMega328P de Microchip:

Programación en Ensamblador, Lenguaje C y un enlace con Arduino

Felipe Santiago Espinosa

ISBN: 978-607-98020-9-7

Universidad Tecnológica de la Mixteca

#### El Microcontrolador ATMega328P de Microchip: Programación en Ensamblador, Lenguaje C y un enlace con Arduino Felipe Santiago Espinosa

Universidad Tecnológica de la Mixteca Km. 2.5 Carretera a Acatlima Huajuapan de León, Oaxaca México

$1^a$  Edición, 19 de noviembre de 2021 ISBN: 978-607-98020-9-7 (R) D.R. 2021 U.T.M.

#### Directorio:

Dr. Modesto Seara Vázquez Rector

Dr. Agustín Santiago Alvarado Vice-Rector Académico

C.P. José Javier Ruiz Santiago Vice-Rector Administrativo

## Índice general

| 1. | Intr | oducción a los Microcontroladores               | 13 |

|----|------|-------------------------------------------------|----|

|    | 1.1. | Sistemas Electrónicos                           | 13 |

|    | 1.2. | Controladores y Microcontroladores              | 14 |

|    | 1.3. | Microprocesadores y Microcontroladores          | 15 |

|    | 1.4. | Microcontroladores y FPGAs                      | 17 |

|    | 1.5. | Organización de los Microcontroladores          | 19 |

|    |      | 1.5.1. La Unidad Central de Procesamiento (CPU) | 19 |

|    |      | 1.5.2. Sistema de Memoria                       | 23 |

|    |      | 1.5.3. Oscilador                                | 25 |

|    |      | 1.5.4. Temporizador/Contador                    | 25 |

|    |      | 1.5.5. Perro Guardián (WDT, watchdog timer)     | 26 |

|    |      | 1.5.6. Puerto Serie                             | 27 |

|    |      | 1.5.7. Entradas y Salidas Digitales             | 27 |

|    |      | 1.5.8. Entradas y Salidas Analógicas            | 28 |

|    | 1.6. | Clasificación de los Microcontroladores         | 28 |

|    | 1.7. | La Tarjeta Arduino                              | 30 |

|    | 1.8. | Sistemas Embebidos e Internet de las Cosas      | 31 |

|    | 1.9. | Ejercicios                                      | 32 |

| 2. |      | Microcontroladores AVR                          | 35 |

|    | 2.1. | Características Generales                       | 35 |

|    | 2.2. | El Núcleo AVR                                   | 37 |

|    |      | 2.2.1. Ejecución de Instrucciones               | 39 |

|    |      | 2.2.2. El Archivo de Registros                  | 39 |

|    | 2.3. | Memoria de Programa                             | 41 |

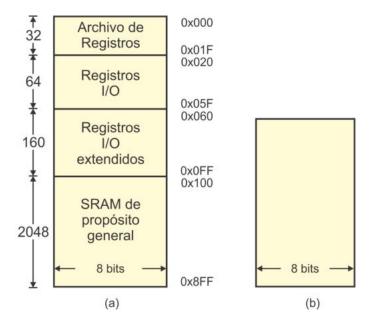

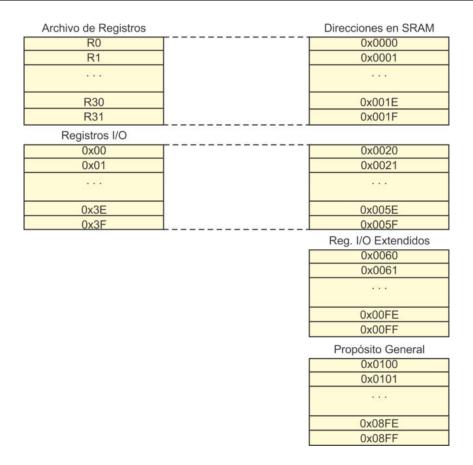

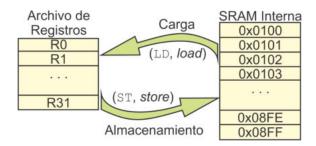

|    | 2.4. | Memoria de Datos                                | 43 |

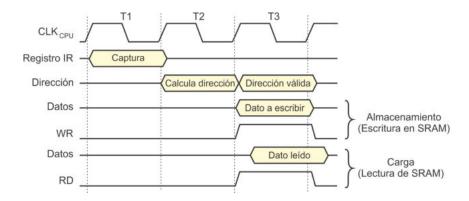

|    |      | 2.4.1. Espacio de SRAM                          | 43 |

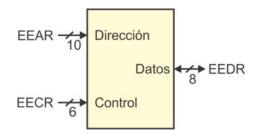

|    |      | 2.4.2. Espacio de EEPROM                        | 49 |

|    | 2.5. | Puertos de Entrada/Salida                       | 52 |

|    | 2.6. | Sistema de Interrupciones                       | 55 |

|    | 2.7. | Inicialización del Sistema (reset)              | 60 |

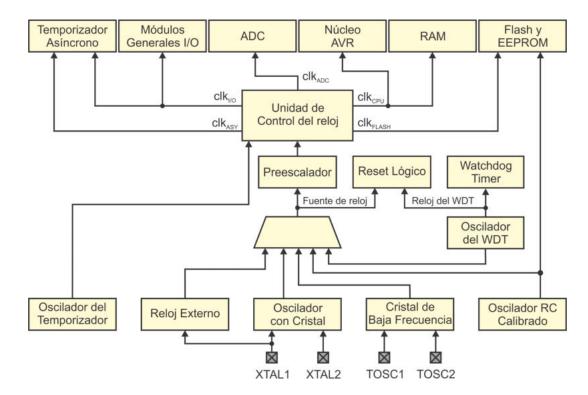

|    | 2.8. | Reloj del Sistema                               | 64 |

|                                  | 2.9.                                          | Modos de Reposo o Bajo Consumo                     |  |

|----------------------------------|-----------------------------------------------|----------------------------------------------------|--|

|                                  | 2.10. El ATMega328P en la Tarjeta Arduino UNO |                                                    |  |

|                                  | 2.11.                                         | Ejercicios                                         |  |

| 3.                               | Prog                                          | gramación de los Microcontroladores 77             |  |

| 3.1. Repertorio de Instrucciones |                                               |                                                    |  |

|                                  |                                               | 3.1.1. Instrucciones Aritméticas y Lógicas         |  |

|                                  |                                               | 3.1.2. Instrucciones para el Control de Flujo      |  |

|                                  |                                               | 3.1.3. Instrucciones de Transferencia de Datos     |  |

|                                  |                                               | 3.1.4. Instrucciones para el Manejo de Bits        |  |

|                                  |                                               | 3.1.5. Instrucciones Especiales                    |  |

|                                  | 3.2.                                          | Modos de Direccionamiento                          |  |

|                                  | 3.3.                                          | Programación en Lenguaje Ensamblador               |  |

|                                  | 3.4.                                          | Programación en Lenguaje C                         |  |

|                                  |                                               | 3.4.1. Tipos de Datos                              |  |

|                                  |                                               | 3.4.2. Operadores Lógicos y para el Manejo de Bits |  |

|                                  |                                               | 3.4.3. Tipos de Memoria                            |  |

|                                  | 3.5.                                          | Programas de Ejemplo                               |  |

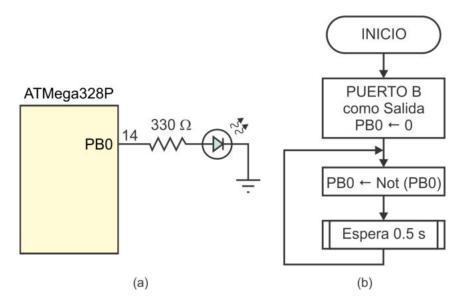

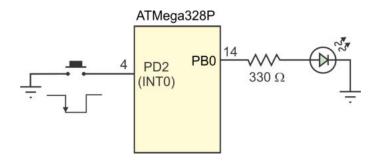

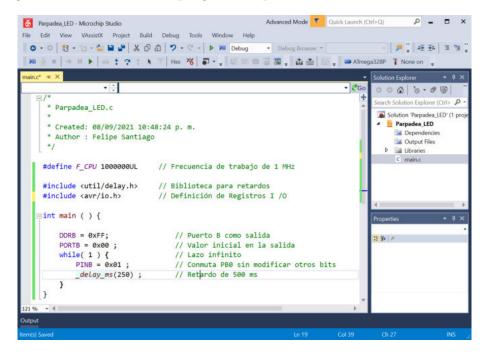

|                                  |                                               | 3.5.1. Parpadeo de un LED                          |  |

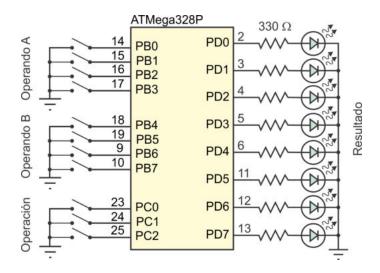

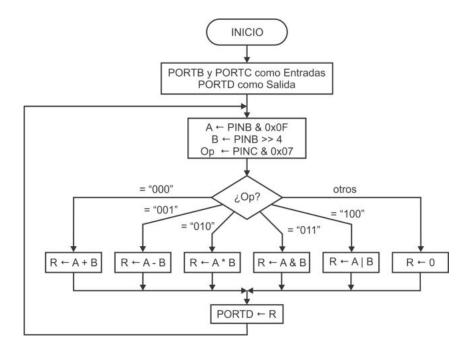

|                                  |                                               | 3.5.2. ALU de 4 Bits                               |  |

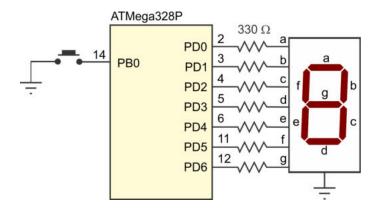

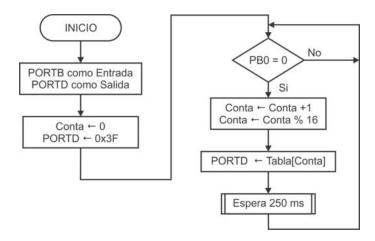

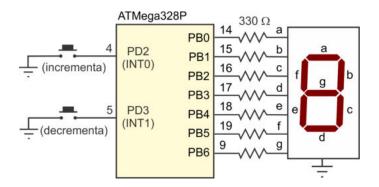

|                                  |                                               | 3.5.3. Contador con Salida en 7 Segmentos          |  |

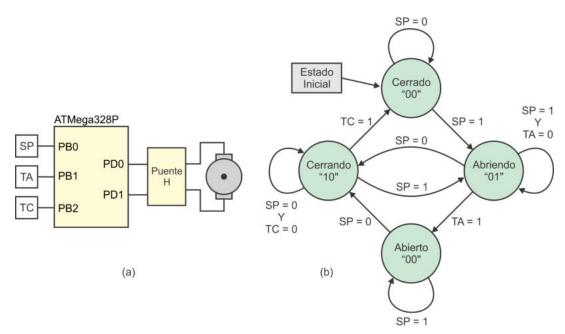

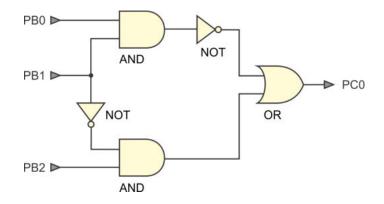

|                                  |                                               | 3.5.4. Máquina de Estados                          |  |

|                                  | 3.6.                                          | Relación entre Lenguaje C y Ensamblador            |  |

|                                  | 3.7.                                          | Manejo de Registros I/O con Arduino                |  |

|                                  | 3.8.                                          | Ejercicios                                         |  |

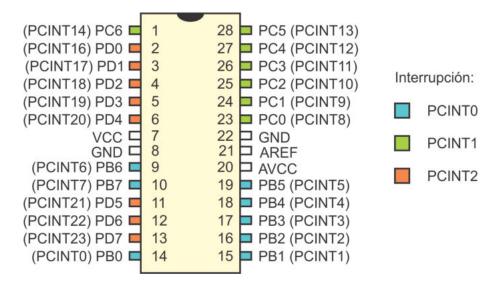

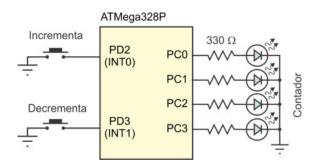

| 4.                               | Inte                                          | rrupciones en los Puertos 127                      |  |

|                                  | 4.1.                                          | Interrupciones Externas                            |  |

|                                  |                                               | 4.1.1. Configuración                               |  |

|                                  |                                               | 4.1.2. Habilitación y Estado                       |  |

|                                  |                                               | 4.1.3. Ejemplos de Uso                             |  |

|                                  | 4.2.                                          |                                                    |  |

|                                  |                                               | 4.2.1. Habilitación y Estado                       |  |

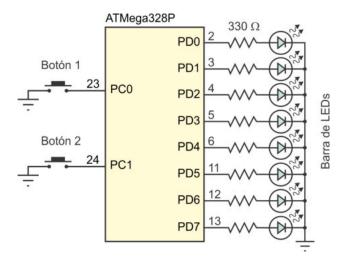

|                                  |                                               | 4.2.2. Ejemplos de Uso                             |  |

|                                  | 4.3.                                          | El atributo <i>volatile</i>                        |  |

|                                  | 4.4.                                          | Manejo de Interrupciones con Arduino               |  |

|                                  | 4.5.                                          | Ejercicios                                         |  |

| <b>5</b> .                       | Tem                                           | aporizadores 147                                   |  |

|                                  | 5.1.                                          | Eventos de los Temporizadores                      |  |

|                                  |                                               | 5.1.1. Desbordamiento                              |  |

|                                  |                                               | 5.1.2. Coincidencia por Comparación                |  |

|                                  |                                               | 5.1.3. Captura de Entrada                          |  |

|    | 7.1.       | Comu      | nicación Serial a través de la USART                 |       | . 223 |

|----|------------|-----------|------------------------------------------------------|-------|-------|

| 7. |            |           | ción Serial (Parte I)                                |       | 223   |

|    | 6.4.       | EJerc10   | cios                                                 | <br>٠ | . 218 |

|    | 6.3.       |           | o del ADC y AC desde Arduino                         |       |       |

|    | 0.0        | 6.2.3.    | Ejemplos con el Comparador Analógico                 |       |       |

|    |            | 6.2.2.    | Registros para el Manejo del AC                      |       |       |

|    |            | 6.2.1.    | Organización del Comparador Analógico                |       |       |

|    | 6.2.       | •         | arador Analógico                                     |       |       |

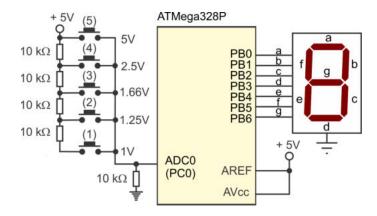

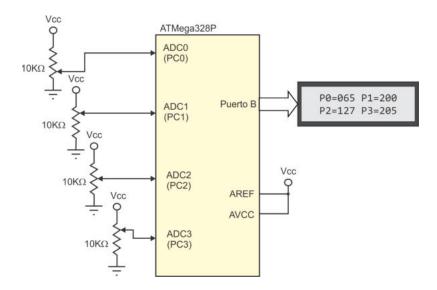

|    |            | 6.1.5.    | Ejemplos con el Convertidor Analógico a Digital      |       |       |

|    |            | 6.1.4.    | El Sensor de Temperatura                             |       |       |

|    |            | 6.1.3.    |                                                      |       |       |

|    |            | 6.1.2.    | El ADC del ATMega328P                                |       |       |

|    |            | 6.1.1.    | 3 1 3 3 1 3 1 3 1 3 1 3 1 3 1 3 1 3 1 3              |       |       |

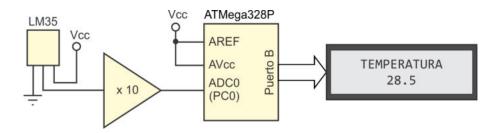

|    | 6.1.       | Conve     | rtidor Analógico a Digital                           |       | . 193 |

| 6. | Maı        | nejo de   | e Información Analógica                              |       | 193   |

|    | 5.10       | . Ejercic |                                                      | <br>• | . 100 |

|    |            |           | emporizadores en Arduno                              |       |       |

|    | 5.0        | 5.8.4.    | Ejemplos con el Temporizador 2                       |       |       |

|    |            | 5.8.3.    | Interrupciones debidas al Temporizador 2             |       |       |

|    |            | 5.8.2.    | Operación Asíncrona del Temporizador 2               |       |       |

|    |            |           | Configuración y Control del Temporizador 2           |       |       |

|    | 5.8.       |           |                                                      |       |       |

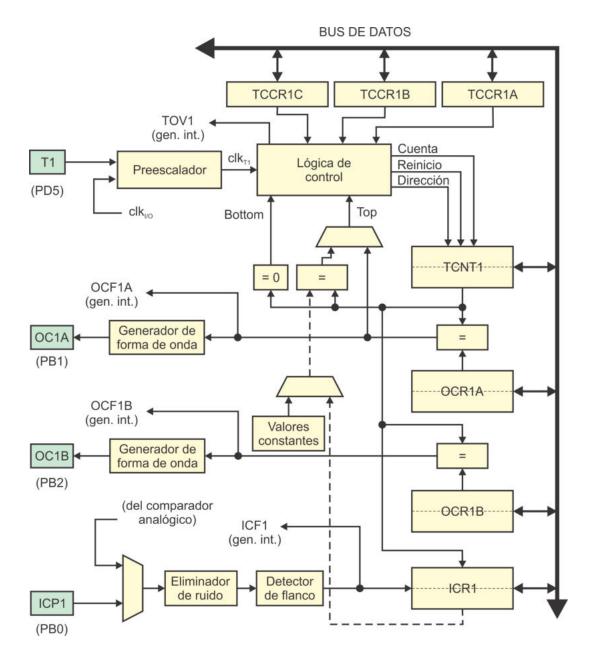

|    | <b>F</b> 0 | 5.7.4.    | Ejemplos con el Temporizador 1                       |       |       |

|    |            | 5.7.3.    | Acceso a los Registros de 16 Bits del Temporizador 1 |       |       |

|    |            | 5.7.2.    | Interrupciones debidas al Temporizador 1             |       |       |

|    |            |           | Configuración y Control del Temporizador 1           |       |       |

|    | 5.7.       |           | aporizador 1                                         |       |       |

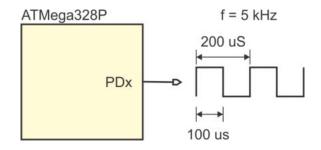

|    |            | 5.6.3.    | Ejemplos con el Temporizador 0                       |       |       |

|    |            | 5.6.2.    | Interrupciones debidas al Temporizador 0             |       |       |

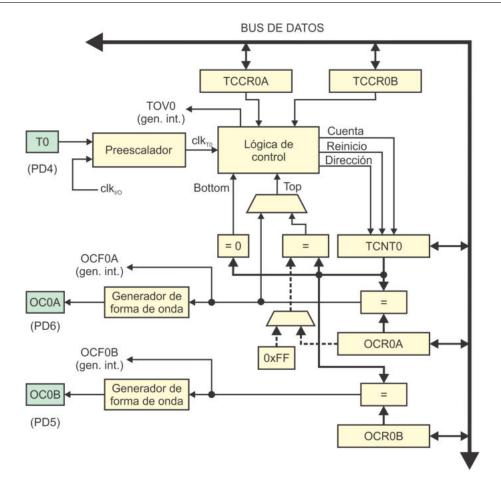

|    |            |           | Configuración y Control del Temporizador 0           |       |       |

|    | 5.6.       |           | nporizador 0                                         |       |       |

|    |            |           | PWM con Fase y Frecuencia Correcta                   |       |       |

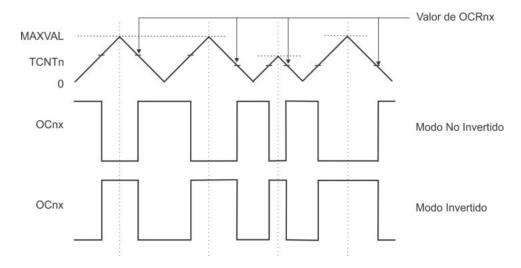

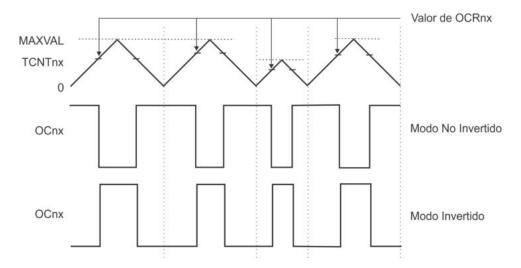

|    |            | 5.5.2.    |                                                      |       |       |

|    |            |           | PWM Rápido                                           |       |       |

|    | 5.5.       |           | ación por Ancho de Pulso (PWM)                       |       |       |

|    | 5.4.       |           | orización Externa                                    |       |       |

|    | 5.3.       |           | alador en los Temporizadores                         |       |       |

|    |            | 5.2.3.    | Respuesta Automática                                 |       |       |

|    |            | 5.2.2.    | Uso de Interrupciones                                |       | . 151 |

|    |            | 5.2.1.    | Sondeo $(Polling)$                                   |       | . 150 |

|    | 5.2.       | Respu     | esta a los Eventos                                   |       | . 150 |

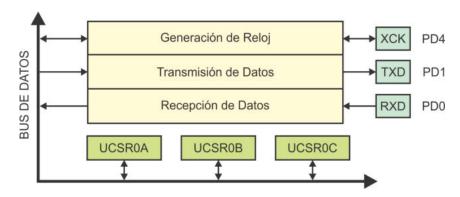

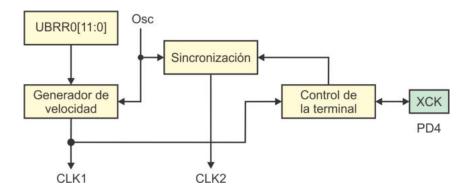

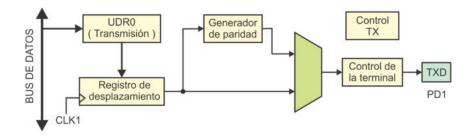

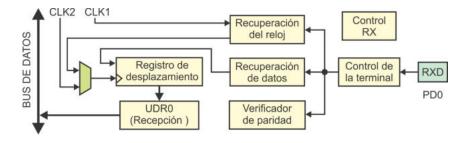

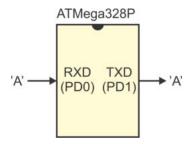

|    |       | 7.1.1.  | Organización de la USART                        | . 225 |

|----|-------|---------|-------------------------------------------------|-------|

|    |       | 7.1.2.  | Registros para el manejo de la USARTO           | . 232 |

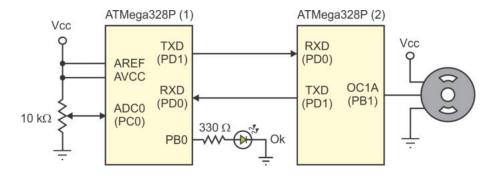

|    |       | 7.1.3.  | Interrupciones debidas a la USARTO              | . 236 |

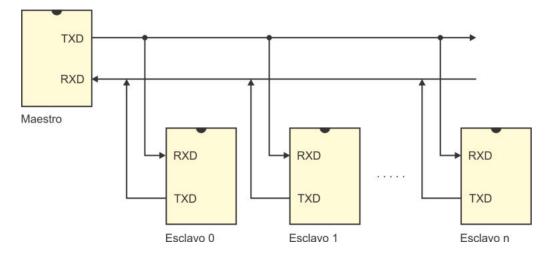

|    |       | 7.1.4.  | Comunicación entre Múltiples Microcontroladores | . 236 |

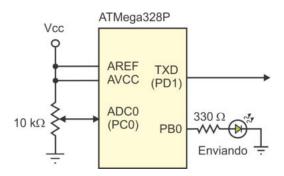

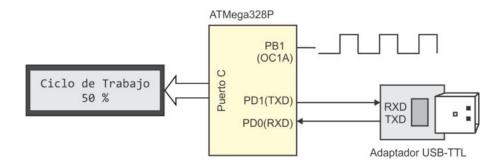

|    |       | 7.1.5.  | Ejemplos de Uso del Módulo USARTO               | . 238 |

|    |       | 7.1.6.  | Envío y Recepción de Datos con Formato          | . 241 |

|    |       | 7.1.7.  | El Módulo USART0 en Arduino                     | . 243 |

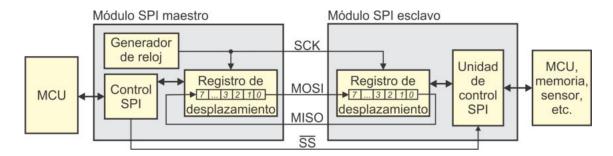

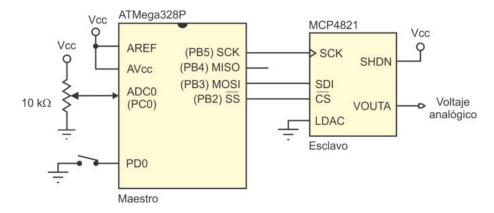

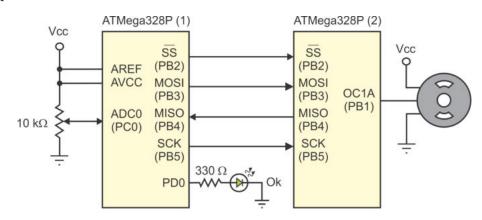

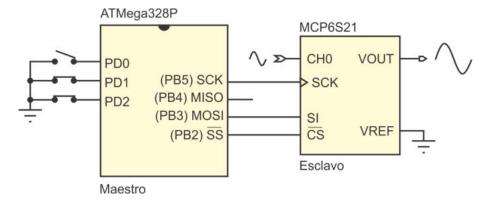

|    | 7.2.  | Comu    | nicación Serial por SPI                         | . 248 |

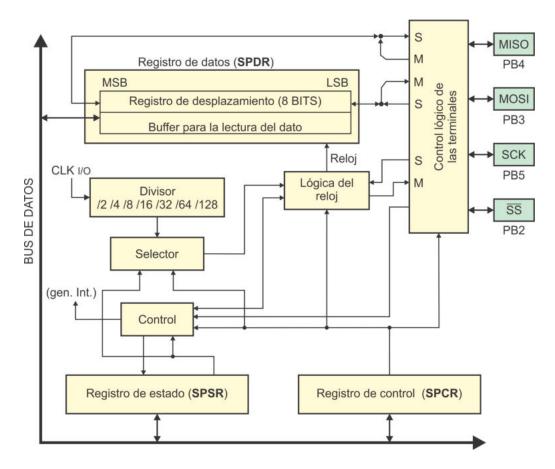

|    |       | 7.2.1.  | Organización de la Interfaz SPI en los AVR      |       |

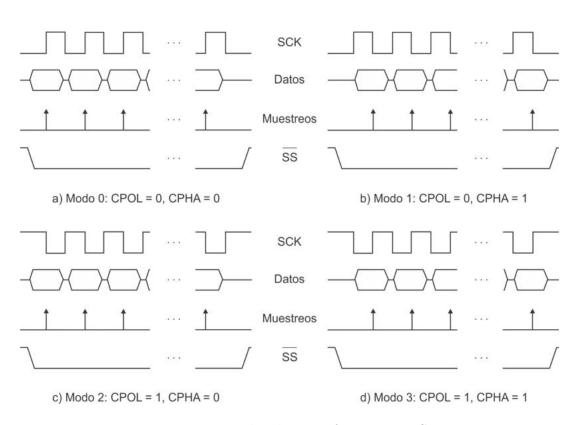

|    |       | 7.2.2.  | Modos de Transferencia por SPI                  | . 251 |

|    |       | 7.2.3.  | Funcionalidad de la Terminal SS                 |       |

|    |       | 7.2.4.  | Registros para el Manejo de la Interfaz SPI     | . 254 |

|    |       | 7.2.5.  | Ejemplos de Uso de la Interfaz SPI              |       |

|    |       | 7.2.6.  | La Interfaz SPI en Arduino                      |       |

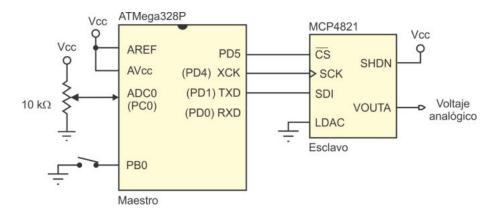

|    | 7.3.  | La US   | ART en Modo SPI Maestro                         |       |

|    |       | 7.3.1.  | Adaptación de los Registros de Control          | . 267 |

|    |       | 7.3.2.  | Uso de la USART en el Modo SPI Maestro          |       |

|    | 7.4.  | Ejercio | zios                                            | . 271 |

|    |       |         |                                                 |       |

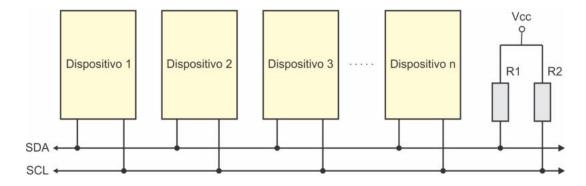

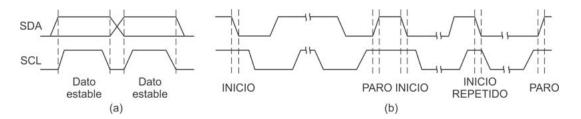

| 8. |       |         | ción Serial (Parte II)                          | 275   |

|    |       |         | ucción                                          |       |

|    | 8.2.  |         | rerencias de Datos vía TWI                      |       |

|    |       |         | Formato de los Paquetes de Dirección            |       |

|    |       | 8.2.2.  | Formato de los Paquetes de Datos                |       |

|    | 0.0   | 8.2.3.  | ı ,                                             |       |

|    | 8.3.  |         | nas Multi-Maestros                              |       |

|    | 8.4.  | _       | ización de la Interfaz TWI en los AVR           |       |

|    |       | 8.4.1.  | Terminales SCL y SDA                            |       |

|    |       | 8.4.2.  | Generador de Velocidad de Transmisión           |       |

|    |       | 8.4.3.  | Unidad de Interfaz con el Bus                   |       |

|    |       |         | Unidad de Comparación de Dirección              |       |

|    |       | 8.4.5.  | Unidad de Control                               |       |

|    | 8.5.  | _       | ros para el manejo de la Interfaz TWI           |       |

|    | 8.6.  |         | s de Transmisión y Códigos de Estado            |       |

|    |       | 8.6.1.  | Modo Maestro Transmisor (MT)                    |       |

|    |       | 8.6.2.  | Modo Maestro Receptor (MR)                      |       |

|    |       | 8.6.3.  | Modo Esclavo Receptor (SR)                      |       |

|    |       | 8.6.4.  | Modo Esclavo Transmisor (ST)                    |       |

|    |       | 8.6.5.  | Estados Misceláneos                             |       |

|    | 8.7.  | -       | ción en Modo Maestro                            |       |

|    | 8.8.  | -       | olos de Uso de la Interfaz TWI                  |       |

|    | 8.9.  |         | erfaz TWI en Arduino                            |       |

|    | 8.10. | Ejerci  | cios                                            | . 314 |

|    |       |         |                                                 |       |

| 9. | $\mathbf{Rec}$ | ursos Especiales                                                              | 319   |

|----|----------------|-------------------------------------------------------------------------------|-------|

|    | 9.1.           | Modos de bajo consumo                                                         | . 319 |

|    | 9.2.           | El perro guardián (WDT, watchdog timer)                                       | . 322 |

|    |                | 9.2.1. Registro para el Manejo del WDT                                        | . 324 |

|    |                | 9.2.2. Configuración del WDT                                                  | . 324 |

|    | 9.3.           | Sección de Arranque en la Memoria Flash                                       |       |

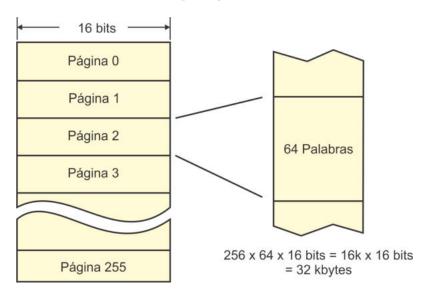

|    |                | 9.3.1. Organización de la Memoria Flash                                       | . 328 |

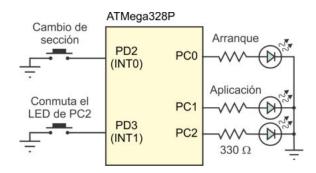

|    |                | 9.3.2. Acceso a la Sección de Arranque                                        | . 329 |

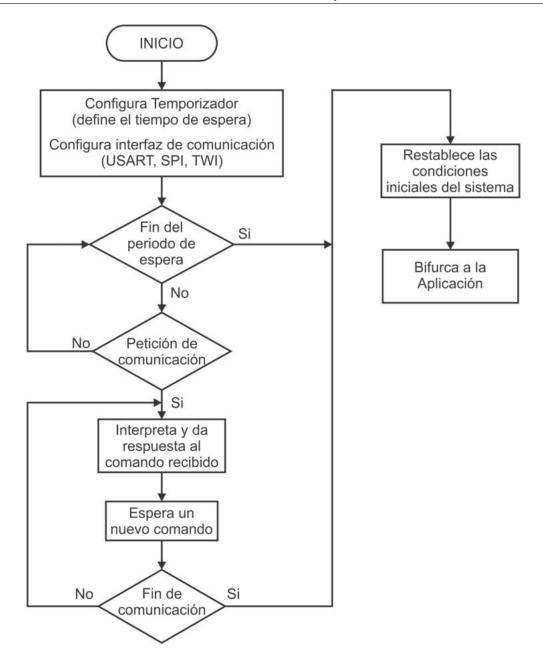

|    |                | 9.3.3. Cargador para Autoprogramación                                         | . 333 |

|    | 9.4.           | Bits de Configuración y Seguridad                                             | . 342 |

|    |                | 9.4.1. Acceso a los Fusibles desde una Aplicación                             | . 346 |

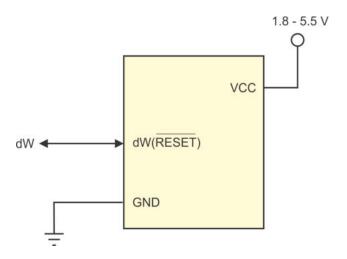

|    | 9.5.           | La interfaz debugWire                                                         | . 346 |

|    |                | 9.5.1. Puntos de Ruptura                                                      | . 348 |

|    |                | 9.5.2. Registro de Depuración                                                 | . 348 |

|    |                | 9.5.3. Limitaciones de la Interfaz debugWire                                  | . 348 |

|    | 9.6.           | Ejercicios                                                                    | . 349 |

| 10 | .Mar           | nejo de Dispositivos Externos                                                 | 351   |

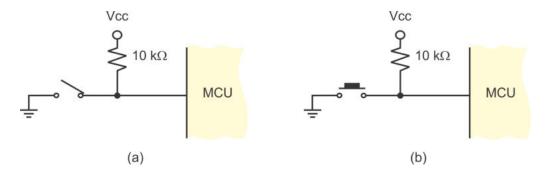

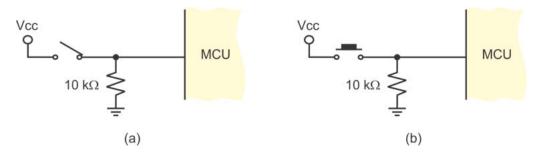

|    | 10.1.          | Interruptores y Botones                                                       | . 351 |

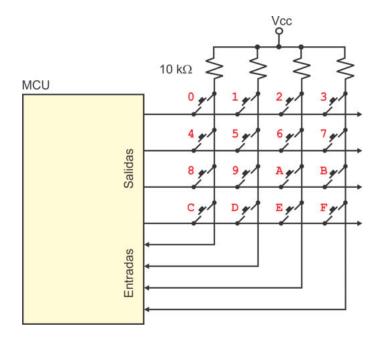

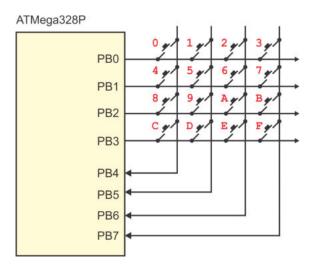

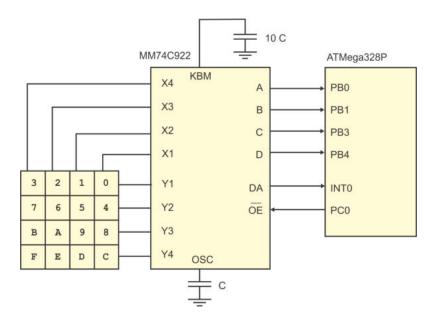

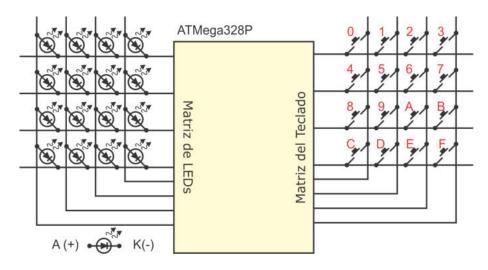

|    | 10.2.          | Teclado Matricial                                                             | . 352 |

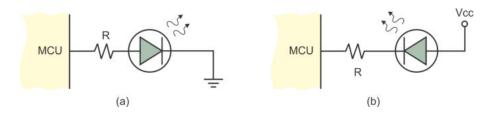

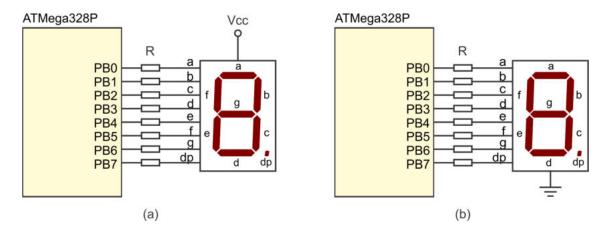

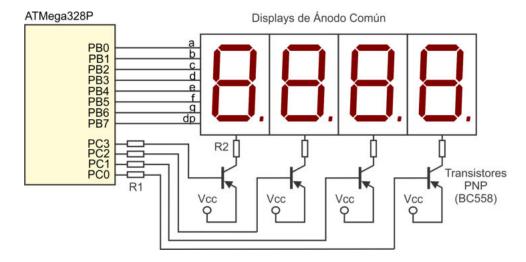

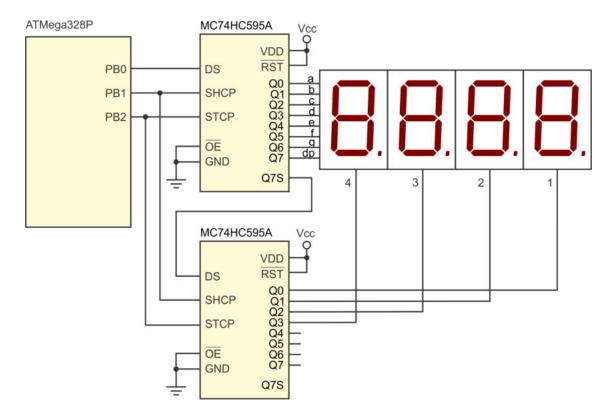

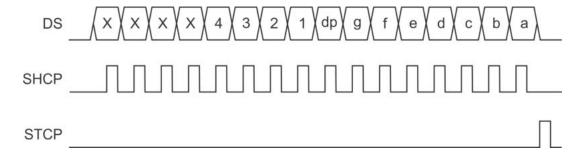

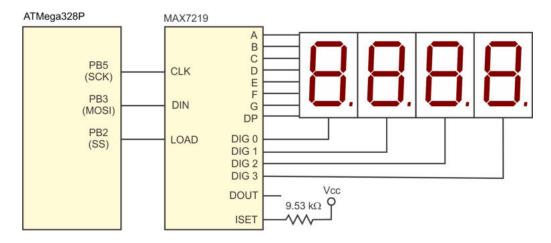

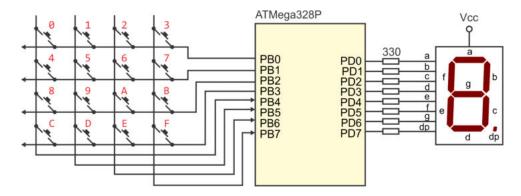

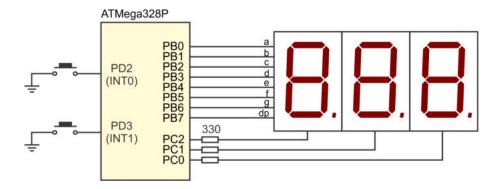

|    | 10.3.          | LEDs y Displays de 7 Segmentos                                                | . 356 |

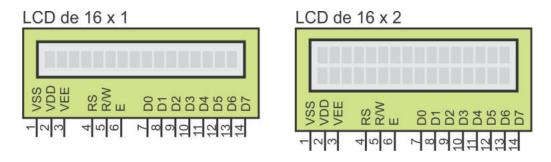

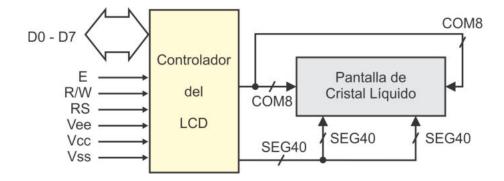

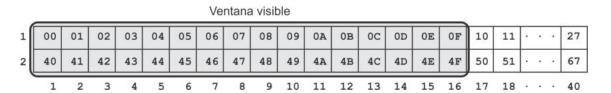

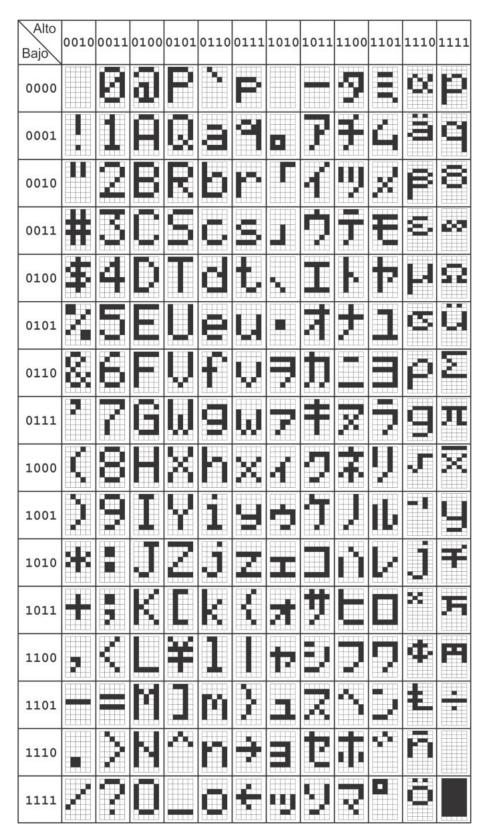

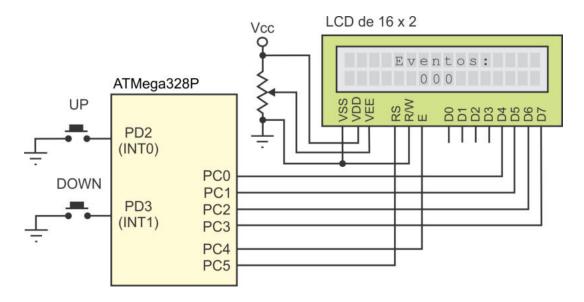

|    | 10.4.          | Manejo de un Display de Cristal Líquido                                       | . 362 |

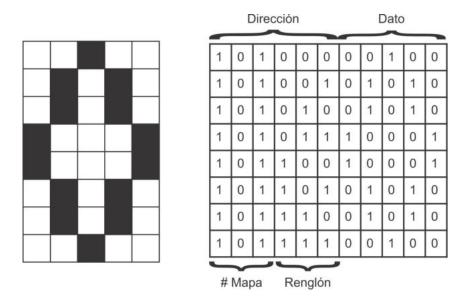

|    |                | $10.4.1.$ Espacios de Memoria en el Controlador de un LCD $\ \ldots \ \ldots$ | . 364 |

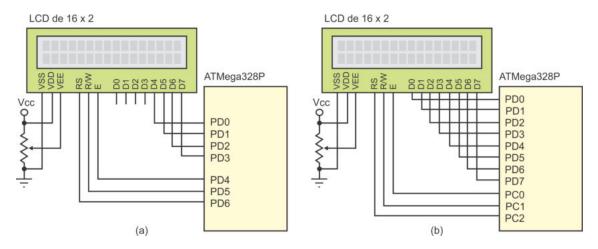

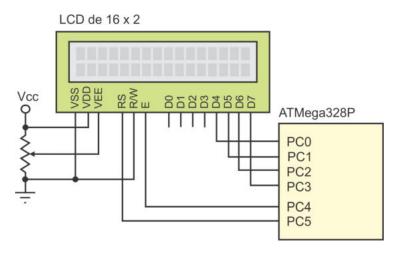

|    |                | 10.4.2. Conexión de un LCD con un Microcontrolador                            | . 368 |

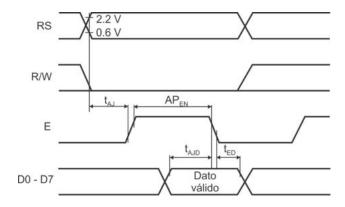

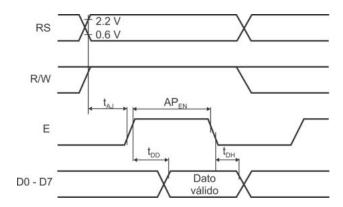

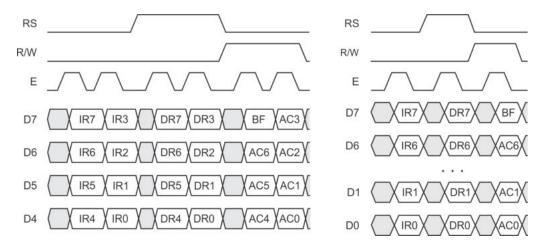

|    |                | 10.4.3. Ciclos de Escritura y Lectura en un LCD                               | . 368 |

|    |                | 10.4.4. Comandos para el Manejo de un LCD                                     | . 371 |

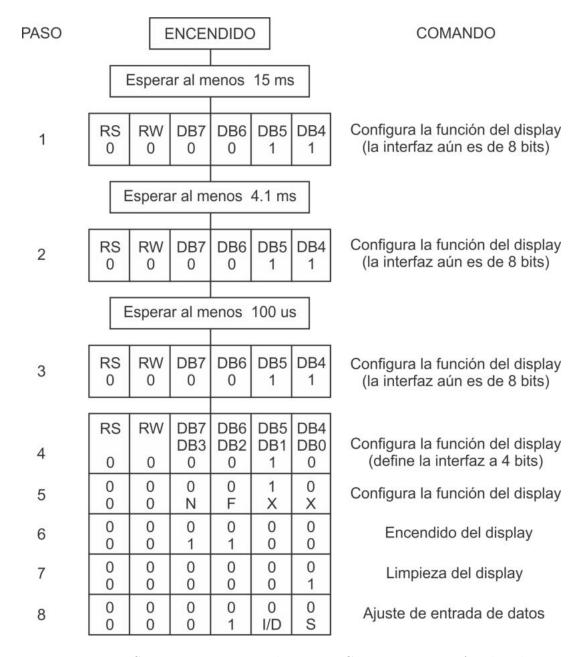

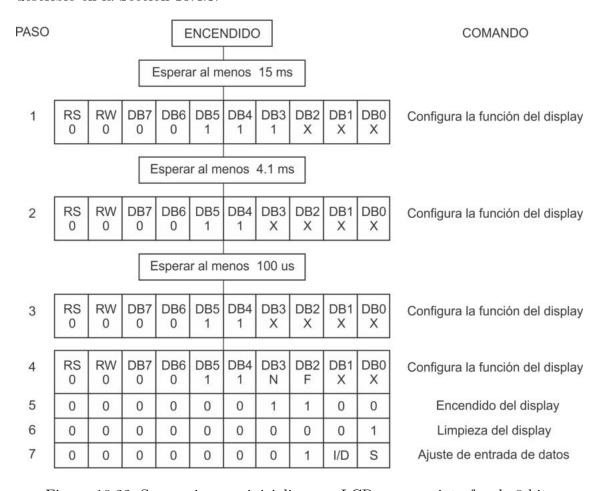

|    |                | 10.4.5. Inicialización del LCD                                                | . 374 |

|    |                | 10.4.6. Biblioteca para el Manejo de un LCD                                   | . 376 |

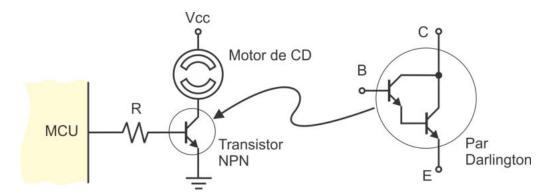

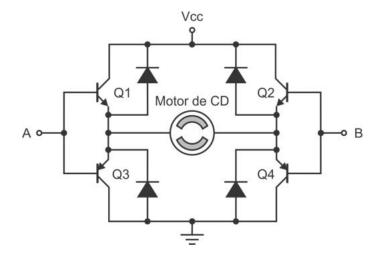

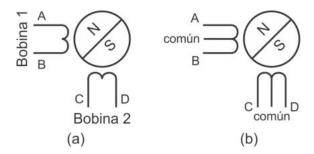

|    | 10.5.          | Manejo de Motores                                                             |       |

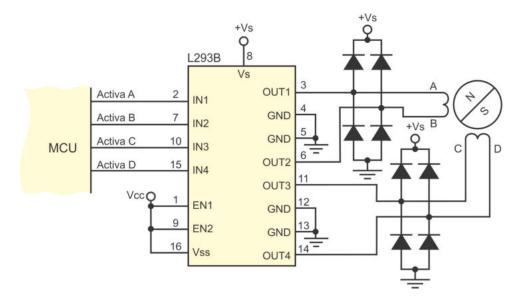

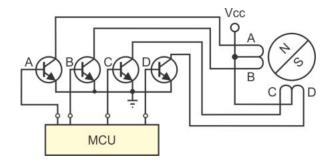

|    |                | 10.5.1. Motores de Corriente Directa                                          | . 382 |

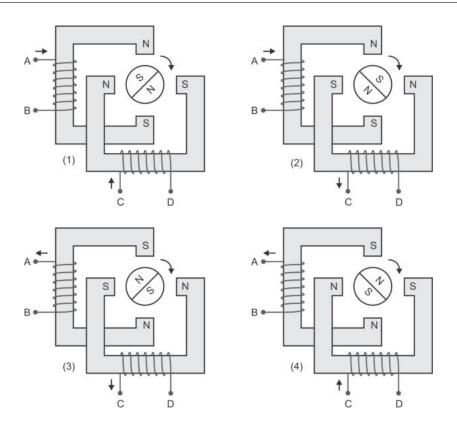

|    |                | 10.5.2. Motores Paso a Paso                                                   | . 384 |

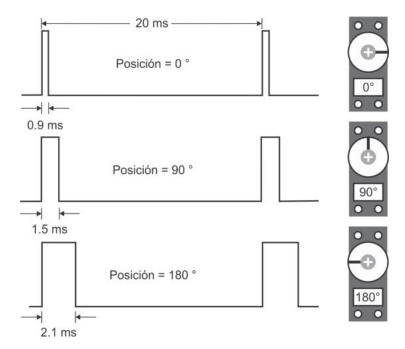

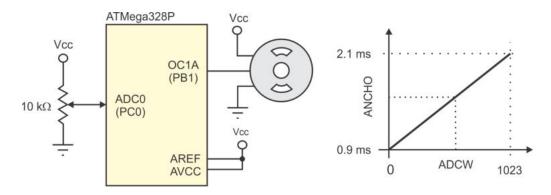

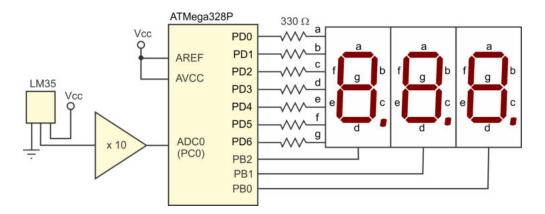

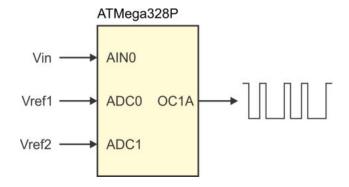

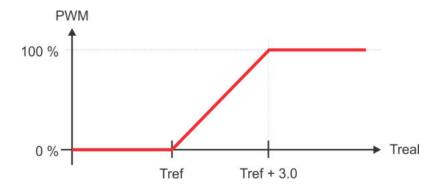

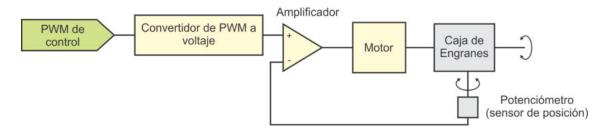

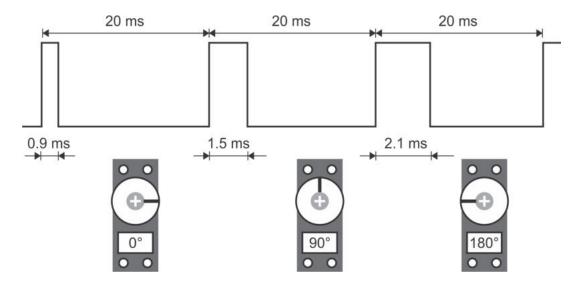

|    |                | 10.5.3. Servomotores                                                          | . 390 |

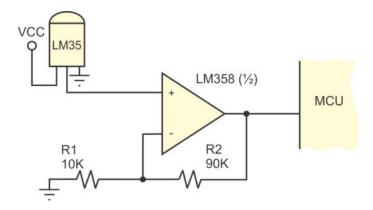

|    | 10.6.          | Interfaz con Sensores                                                         | . 391 |

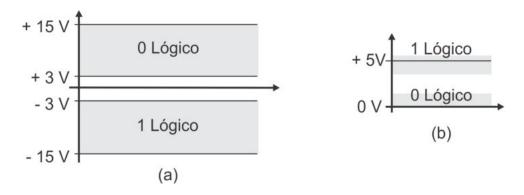

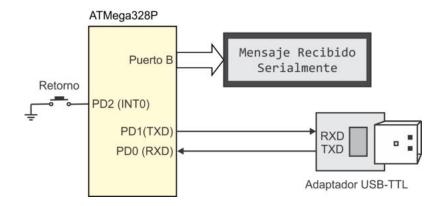

|    | 10.7.          | . Interfaz con una Computadora Personal                                       | . 393 |

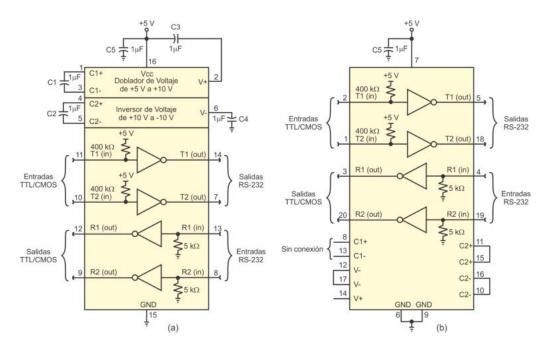

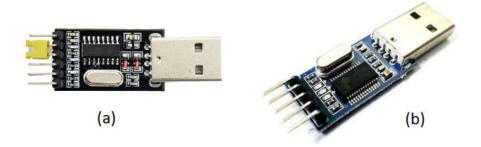

|    |                | 10.7.1. Cable Adaptador de USB a RS-232                                       | . 394 |

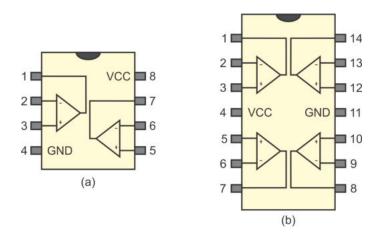

|    |                | 10.7.2. Circuitos Integrados Controladores                                    | . 395 |

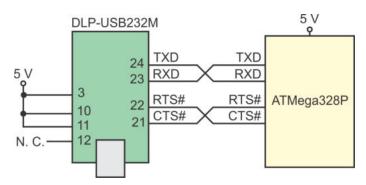

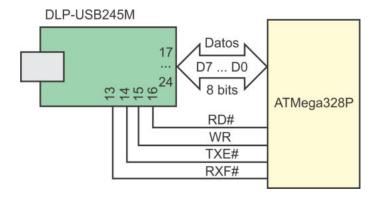

|    |                | 10.7.3. Adaptadores de USB a TTL                                              | . 397 |

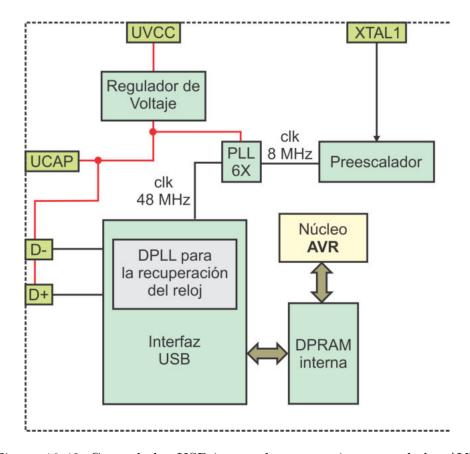

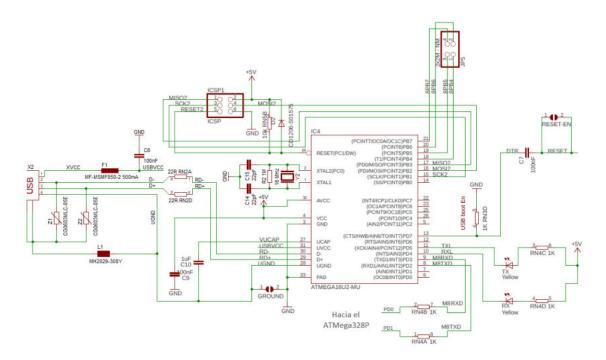

|    |                | 10.7.4. AVR con Controlador USB Integrado                                     | . 398 |

|    | 10.8.          | Ejercicios                                                                    | . 400 |

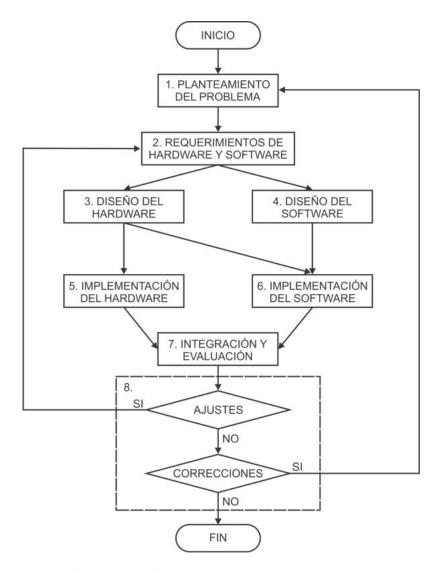

| 11 | .Des           | arrollo de Sistemas                                                           | 405   |

|    | 11.1.          | Metodología de Desarrollo                                                     | . 406 |

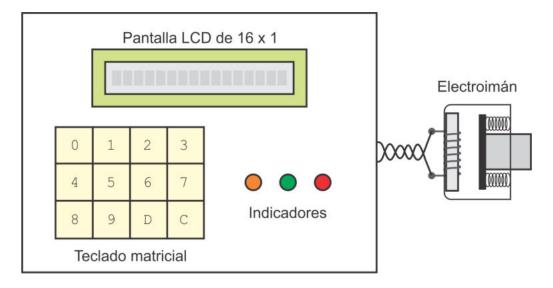

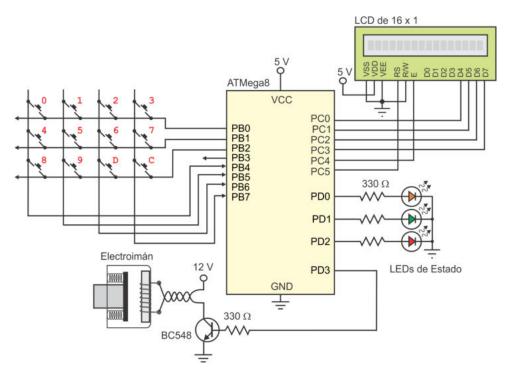

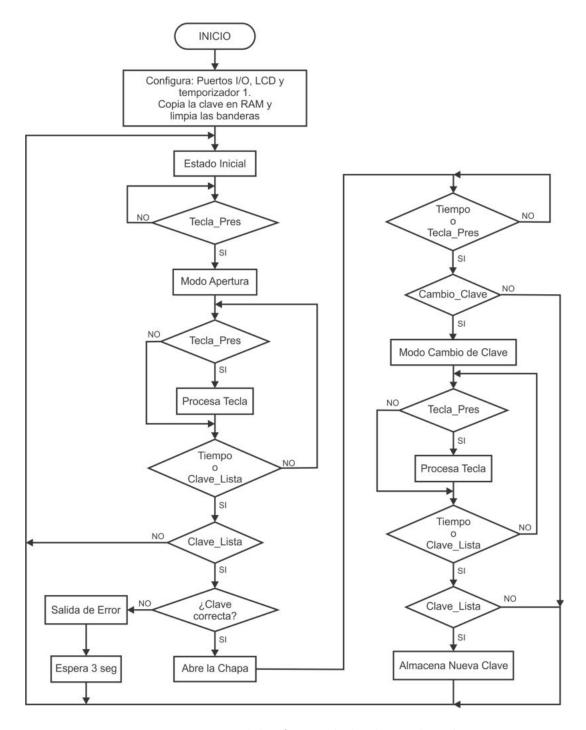

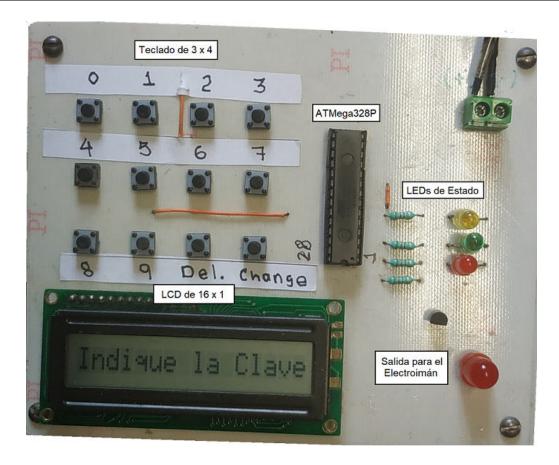

|    | 11.2.          | . Chapa Electrónica                                                           | . 410 |

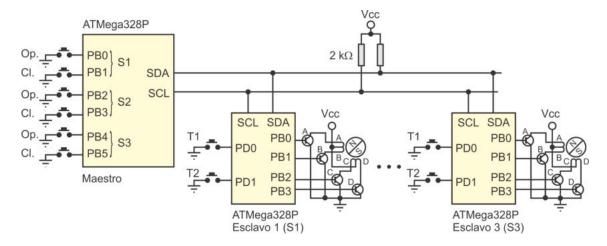

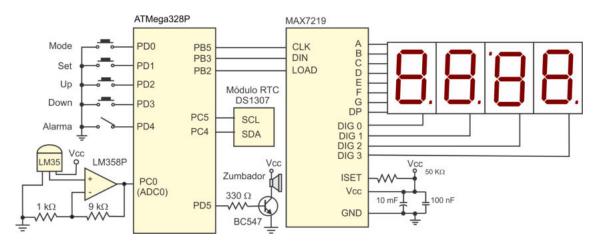

| 11.2.1. Planteamiento del Problema                    | . 410 |

|-------------------------------------------------------|-------|

| 11.2.2. Requerimientos de Hardware y Software         | . 413 |

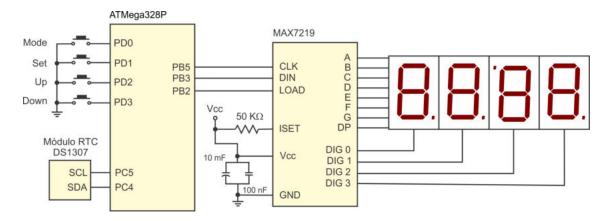

| 11.2.3. Diseño del Hardware                           | . 414 |

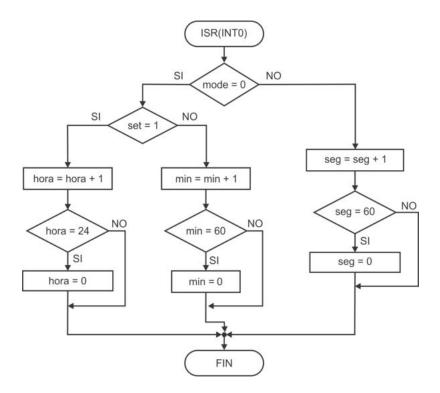

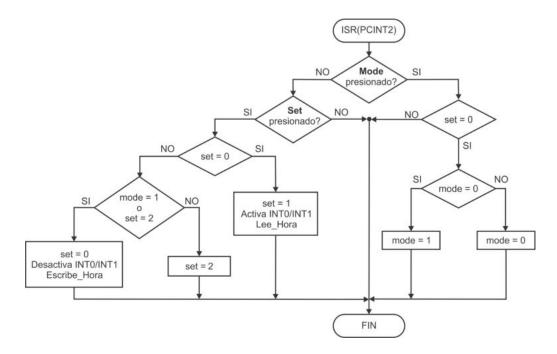

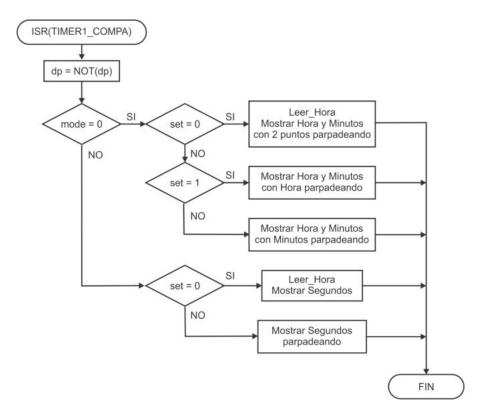

| 11.2.4. Diseño del Software                           | . 414 |

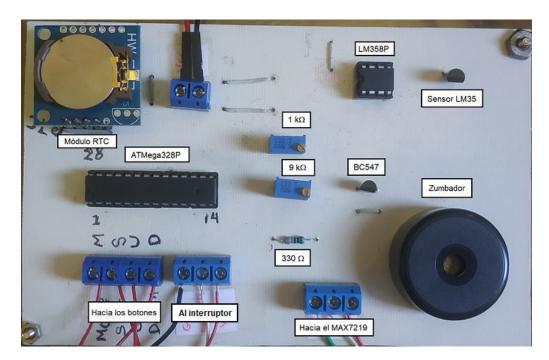

| 11.2.5. Implementación del Hardware                   | . 417 |

| 11.2.6. Implementación del Software                   | . 418 |

| 11.2.7. Integración y Evaluación                      |       |

| 11.2.8. Ajustes y Correcciones                        | . 423 |

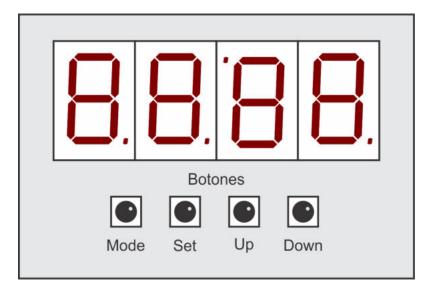

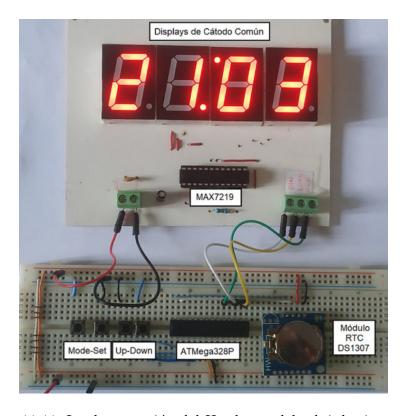

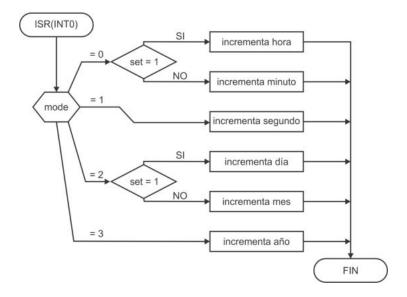

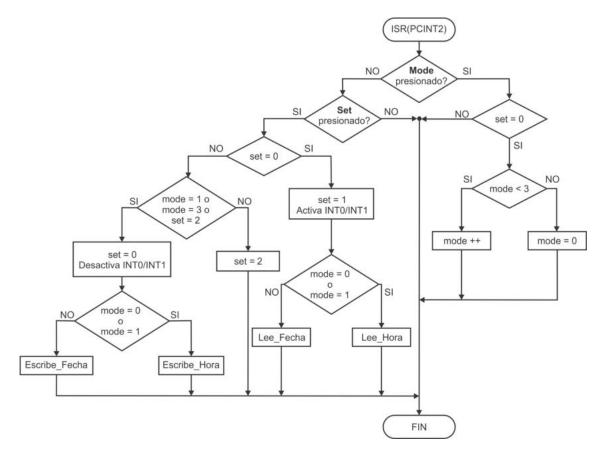

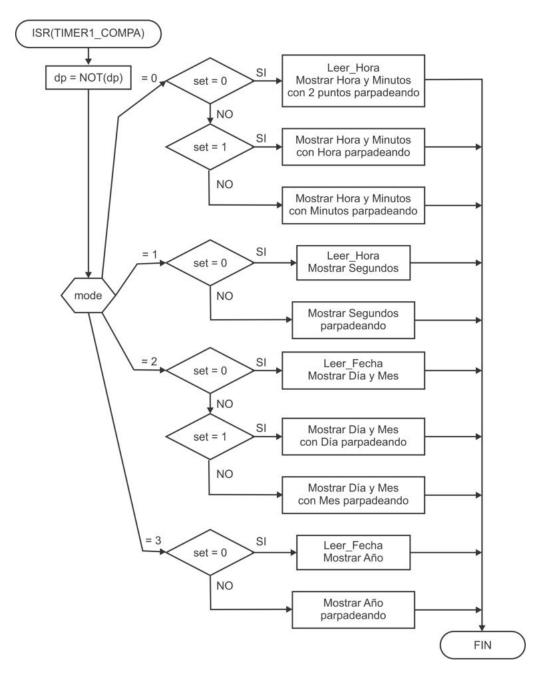

| 11.3. Sistema Embebido Multifunción                   |       |

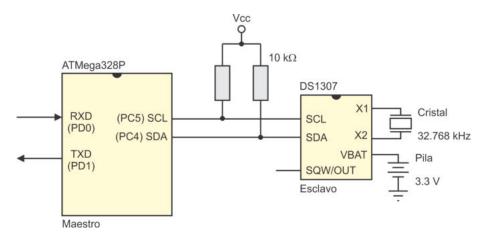

| 11.3.1. Incremento 1: Reloj de Tiempo Real            |       |

| 11.3.2. Incremento 2: Reloj/Calendario de Tiempo Real |       |

| 11.3.3. Incremento 3: Reloj/Calendario con Alarma     | . 444 |

| 11.3.4. Incremento 4: Reloj/Calendario con Alarma y   |       |

| Temporizador                                          | . 450 |

| 11.3.5. Incremento 5: Reloj/Calendario con Alarma,    |       |

| Temporizador y Termómetro                             |       |

| 11.4. Sistemas Propuestos                             | . 462 |

| A. Registros I/O                                      | 469   |

| B. Repertorio de Instrucciones                        | 477   |

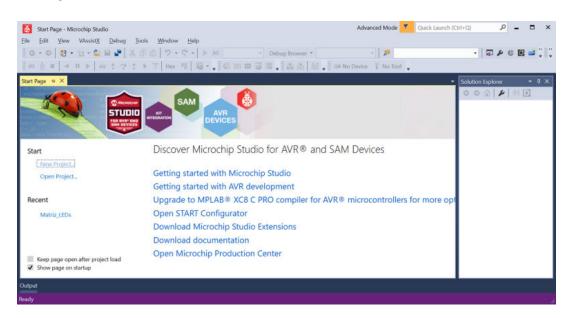

| C. Uso de Microchip Studio                            | 483   |

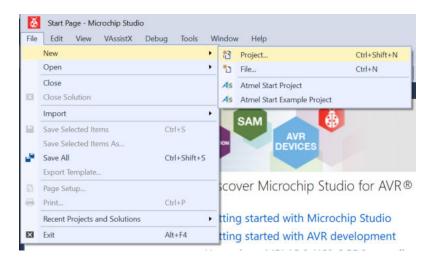

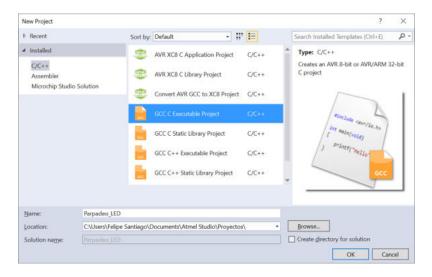

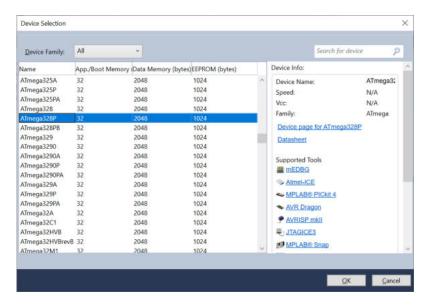

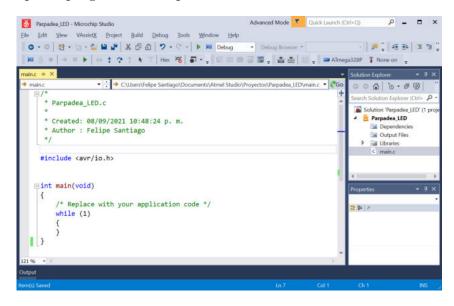

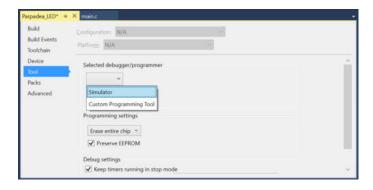

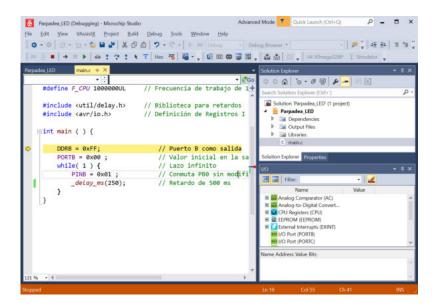

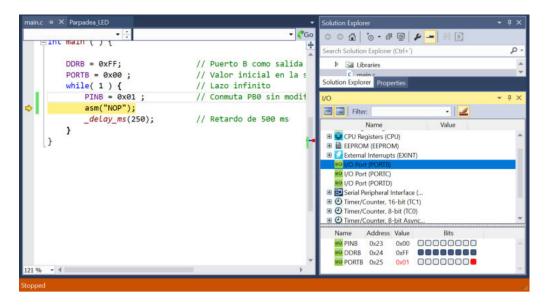

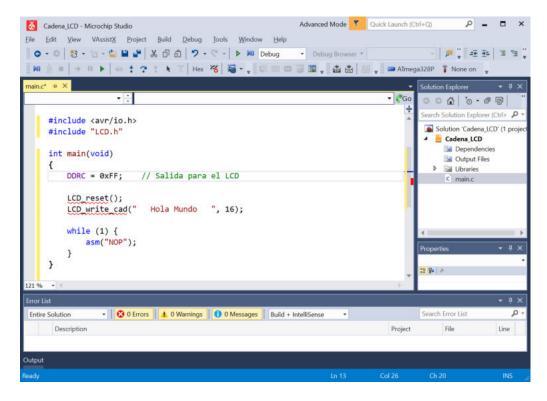

| C.1. Construcción de un Proyecto                      | . 483 |

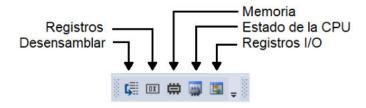

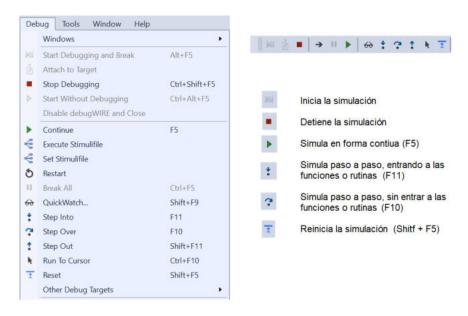

| C.2. Simulación de un Proyecto                        |       |

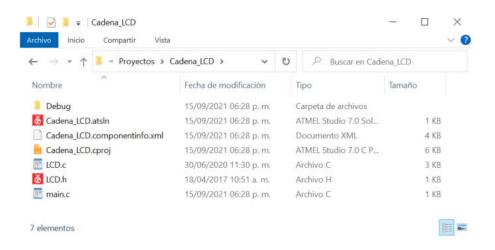

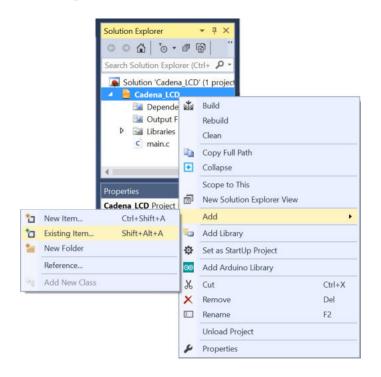

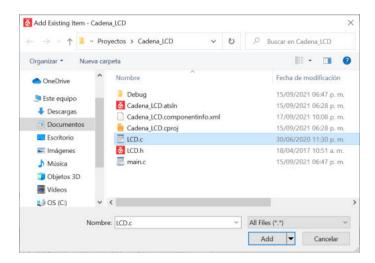

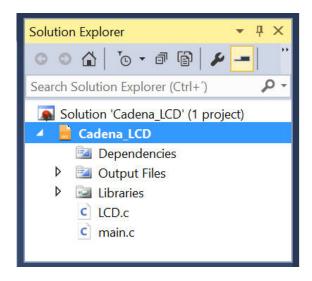

| C.3. Inserción de una Biblioteca de Funciones         |       |

|                                                       |       |

### Prólogo

En el año 2012 la Universidad Tecnológica de la Mixteca me publicó el libro Los Microcontroladores AVR de ATMEL, inicio el presente libro compartiendo su prólogo porque describe la motivación que me llevó a su escritura y este aspecto no ha cambiado. Posteriormente complemento el prólogo haciendo referencia a la nueva versión, enfocada al Microcontrolador ATMega328P.

#### Prólogo: Los Microcontroladores AVR de ATMEL

Comencé a trabajar con microcontroladores en el año de 1994, precisamente en uno de mis últimos cursos de licenciatura. Un microcontrolador también suele ser referido como MCU (*Micro Controller Unit*), por lo que a lo largo del texto indistintamente lo trato de una u otra manera.

El primer MCU que utilicé fue un 8031, un microcontrolador de 8 bits perteneciente a la familia MCS-51 de Intel. El 8031 requiere de todo un sistema de acondicionamiento para ser puesto en marcha. Posteriormente otros microcontroladores llegaron a mis manos, adquirí experiencia trabajando con el DS5000T, una versión mejorada del 8031, con memoria de programa tipo NVRAM (RAM no volátil) y un reloj de tiempo real, pero manufacturado por Dallas Semiconductor. Luego, conocí a la familia de microcontroladores PIC de Microchip, tuve una ligera experiencia con el HC11 de Motorola y en los últimos años he trabajado con los microcontroladores AVR, de ATMEL.

Desde mi incorporación a la Universidad Tecnológica de la Mixteca, en 1998, año con año he impartido el curso de microcontroladores, utilizando uno u otro dispositivo, según la disponibilidad o requerimientos de las aplicaciones. Con la experiencia adquirida he observado que los microcontroladores AVR tienen más recursos en relación con sus equivalentes en costo de otras compañías, además de un rendimiento más alto.

Por ello, desde el año 2006 he enfocado mis cursos al manejo de los microcontroladores AVR, específicamente trabajando con el ATMega8 y el ATMega16. El primer paso para trabajar con estos dispositivos fue la búsqueda del libro de texto adecuado. Necesitaba un libro que detallara al hardware y lo vinculara con el software,

10 PRÓLOGO

que sentara las bases para el desarrollo de sistemas y permitiera a los estudiantes empezar desde cero en los microcontroladores, hasta adquirir ideas aplicables al desarrollo de sistemas complejos. Y que además incluyera aspectos relacionados con su programación, tanto en Ensamblador como en Lenguaje C. Al no encontrarlo me di a la tarea de escribirlo.

En este libro pretendo reflejar la experiencia que he adquirido con estos dispositivos. Es un libro de texto básico, inicialmente para mis cursos y más adelante, quizás, también sea empleado en otras universidades o por profesionistas independientes interesados en este apasionante mundo de los microcontroladores.

Dado que el tema central son los microcontroladores, supongo que los lectores tienen fundamentos de electrónica digital, esto involucra un conocimiento de sistemas numéricos, compuertas lógicas, registros, memorias, máquinas de estados, etc., incluso algunos aspectos básicos de programación en ensamblador y en Lenguaje C, u otro lenguaje de alto nivel. Por lo tanto, me enfoco en las características de los microcontroladores y, sólo si es necesario, profundizo en algún concepto en torno a ellos, pero sin desviarme del tema de interés.

A lo largo del texto realizo una descripción del hardware y el software de los micro-controladores ATMega8 y ATMega16, mostrando como los diferentes recursos del MCU pueden ser manejados en Ensamblador o en Lenguaje C. Este es un aspecto interesante, dado que pretendo mostrar las ventajas o inconvenientes de desarrollar aplicaciones en diferentes niveles de programación. Para todos los recursos internos he documentado ejemplos completos, los cuales fueron previamente implementados como prácticas en la Universidad Tecnológica de la Mixteca.

Dispongo de un capítulo dedicado al manejo de dispositivos externos y concluyo con la propuesta de una metodología que se puede emplear para construir sistemas con más requerimientos, la cual ilustro con el desarrollo de dos sistemas relativamente complejos.

Agradezco a la Universidad Tecnológica de la Mixteca las facilidades para llevar a cabo la redacción de este libro, deseo sea de utilidad para las futuras generaciones de esta y otras instituciones. También agradezco a todos los alumnos y profesores que, de una u otra manera, colaboraron en la realización y revisión de este texto.

#### Prólogo a la versión ATMega328P

Actuamente la empresa ATMEL es parte de Microchip, otro fabricante de microcontroladores y dispositivos electrónicos, quien clasifica su gama de microcontroladores de 8 bits en dos familias: Los PIC y los AVR.

Un par de años posteriores a la publicación del primer libro se popularizó el uso de la tarjeta Arduino, una plataforma que facilita el diseño de sistemas con el mínimo de

PRÓLOGO 11

conocimientos sobre los microcontroladores. La tarjeta Arduino inició soportada por un ATMega8, pero pasó poco tiempo para que migrara al ATMega328P, por tener más memoria y recursos adicionales que aumentan su capacidad de procesamiento.

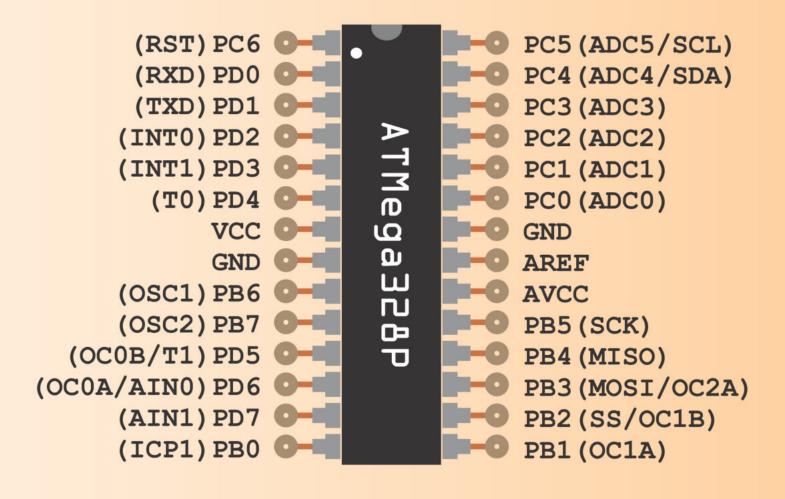

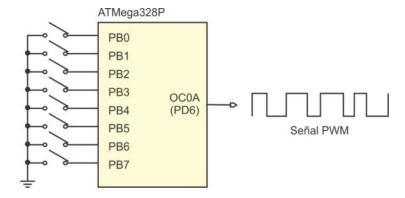

El ATMega328P tiene la misma disposición de pines que el ATMega8, las diferencias principales entre ellos son: incluye 32 kbytes para memoria de código, todas las terminales pueden generar interrupciones y los tres temporizadores tienen dos registros de comparación, pudiendo generar respuesta automática en seis terminales diferentes, lo que significa que un ATMega328P puede generar hasta seis señales PWM en forma simultánea.

Por ello, desde el año 2016 utilizó al ATMega328P para mis cursos de Microcontroladores. El incremento en recursos hizo necesaria la inclusión de nuevos registros o el cambio en la estructura de los existentes, por lo tanto, un programa realizado para un ATMega8 puede no funcionar en un ATMega328P. De manera que fue necesario actualizar el libro de texto y el resultado ahora ha llegado a tus manos.

Si bien es cierto que la tarjeta Arduino facilita el desarrollo de aplicaciones, en la medida en que los desarrolladores avanzan sus diseños tienen requerimientos especiales, como el uso simultáneo de recursos atendidos por interrupciones o configuraciones distintas a las establecidas por el entorno, por ejemplo, la generación de una señal PWM con una frecuencia variable. Para esos casos, se debe entender la organización del microcontrolador y hacer un manejo directo de los registros de configuración, sin la envoltura que proporciona Arduino.

La buena noticia es que el código C desarrollado para un ATMega328P puede incluirse dentro de un *Sketch* de Arduino y se ejecutará sin inconveniente. Para algunos ejemplos del texto se muestra cómo se puede ralizar este híbrido, introduciendo código C para simplificar o personalizar el manejo de recursos.

Nuevamente agradezco a la Universidad Tecnológica de la Mixteca porque sigo perteneciendo a esta gran institución y a todas las personas que se tomaron un minuto para felicitarme por la escritura del primer libro, con mucho agrado y satisfacción vi que se utilizó en diferentes instituciones de México y que llegó a paises hermanos, como Perú, Chile, Colombia, Cuba y República Dominicana. Esa fue la motivación para la adaptación del libro al microcontrolador ATMega328P, fue satisfactorio revisar el correo electrónico y encontrarme con la noticia de que hubo alguien en algún lugar distante a quien le sirvió el libro, espero ocurra lo mismo con este nuevo material y que sigan llegando los correos.

Felipe Santiago Espinosa fsantiag@mixteco.utm.mx

### Capítulo 1

## Introducción a los Microcontroladores

En este capítulo se da una introducción al tema, exponiendo conceptos generales, es decir, conceptos que no están enfocados a un MCU particular. Se describen los alcances y limitaciones de estos dispositivos y se muestra una organización común a la mayoría de microcontroladores.

#### 1.1. Sistemas Electrónicos

La electrónica ha evolucionado de manera sorprendente en los últimos años, tanto que actualmente no es posible concebir la vida sin los sistemas electrónicos. Los sistemas electrónicos son una parte fundamental en el trabajo de las personas, proporcionan entretenimiento y facilitan las actividades en los hogares.

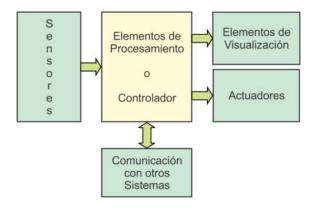

Un sistema electrónico puede ser representado con el diagrama de la Figura 1.1, sin importar la funcionalidad para la cual fue diseñado. El sistema recibe las peticiones de los usuarios o conoce lo que ocurre en su entorno por medio de los sensores. Los sensores son dispositivos electrónicos que se encargan de acondicionar diferentes tipos de información a un formato reconocido por los elementos de procesamiento. Un sensor puede ser tan simple como un botón o tan complejo como un reconocedor de huella digital, pero si los elementos de procesamiento son digitales, en ambos casos la salida va a estar codificada en 1's y 0's. Con los sensores se pueden monitorear diferentes parámetros, como: temperatura, humedad, velocidad, intensidad luminosa, etc.

Los elementos de visualización son dispositivos electrónicos que muestran el estado actual del sistema, esta información le permite al usuario tomar decisiones. Algunos elementos de visualización son: LEDs individuales o matrices de LEDs, displays de 7 segmentos o de cristal líquido.

Figura 1.1: Abstracción de un sistema electrónico

Los actuadores son dispositivos electrónicos o electromecánicos que también forman parte de las salidas de un sistema, pero con la capacidad de modificar el entorno, es decir, van más allá de la visualización, algunos ejemplos son: motores, electroválvulas, relevadores, etc.

Los elementos de comunicación proporcionan a un sistema la capacidad de enlazarse con otros, son necesarios cuando varios sistemas deben coordinarse para realizar una tarea compleja. Cada sistema tiene sus elementos de procesamiento y está orientado a resolver una etapa específica, es a través de protocolos predefinidos como se establece la comunicación entre sistemas.

Los elementos de procesamiento son un conjunto de dispositivos electrónicos que determinan la funcionalidad del sistema con el desarrollo de uno o varios procesos, también se les refiere como el **Controlador** o la **Tarjeta de Control** del sistema. El **Controlador** recibe la información proveniente de los sensores, evalúa el estado actual del sistema y genera resultados visuales, activa algún actuador o notifica sobre nuevas condiciones a otro sistema.

#### 1.2. Controladores y Microcontroladores

El concepto de controlador ha permanecido invariable a través del tiempo, aunque su implementación física ha cambiado con los avances tecnológicos. Los controladores de los primeros sistemas electrónicos se construyeron con base en circuitos analógicos, las decisiones se tomaban con diferentes configuraciones de transistores o amplificadores operacionales. En los setentas se empleaba lógica discreta con circuitos digitales de baja o mediana escala de integración.

El primer microprocesador (4004 de Intel) fue puesto en operación en 1971, esto permitió el desarrollo de las tarjetas de control con un microprocesador y sus elementos de soporte (memoria, entrada/salida, etc.). A estas tarjetas también se les conoce como Computadoras en una Sola Tarjeta (SBC, single board computer).

Figura 1.2: Los microcontroladores remplazan tarjetas con varios CI

Actualmente se han integrado todos estos elementos en un circuito integrado único y a este se le refiere como **Unidad Micro Controladora** (MCU, *Micro Controller Unit*) o simplemente como **Microcontrolador**, esta integración se ilustra en la Figura 1.2.

Un **Microcontrolador** es un circuito con una escala de integración muy grande (VLSI¹, very large scale integration) que internamente contiene una Unidad Central de Procesamiento (CPU, Central Processing Unit), memoria para código, memoria para datos, temporizadores, fuentes de interrupción y otros recursos necesarios para el desarrollo de aplicaciones, por lo general con un propósito específico.

A pesar de que un MCU incluye los elementos necesarios para ser considerado como una computadora en un circuito integrado, frecuentemente no es tratado como tal porque su uso típico consiste en el desempeño de funciones de "control" interactuando con el "mundo real" para monitorear condiciones (a través de sensores) y en respuesta a ello, encender o apagar dispositivos (por medio de actuadores).

#### 1.3. Microprocesadores y Microcontroladores

Ocasionalmente estos dispositivos se tratan como iguales, sin embargo, existen diferencias fundamentales a considerar. Un microprocesador básicamente contiene una CPU mientras que un microcontrolador además de la CPU contiene memoria, temporizadores, manejador de interrupciones y otros recursos útiles para el desarrollo de aplicaciones, todos estos elementos en un circuito integrado.

El microcontrolador tiene más recursos que el microprocesador pero su CPU está limitada en términos de su capacidad de procesamiento. Las limitaciones principales son:

• Velocidad de procesamiento: Actualmente los microcontroladores de gama baja trabajan a frecuencias cercanas a 20 MHz, mientras que los microprocesadores están trabajando en el orden de GHz.

<sup>&</sup>lt;sup>1</sup>Circuitos integrados con más de 10,000 transistores

- Capacidad de direccionamiento: Un microcontrolador promedio dispone de 8 Kbytes para instrucciones y 1 Kbyte para datos, en contraste con el espacio que pueden direccionar los microprocesadores modernos, este está en el orden de Terabytes y es compartido por instrucciones y datos. Por ello, el repertorio de instrucciones de los microprocesadores debe incluir modos de direccionamiento que les permitan este alcance.

- Tamaño de los datos: Los microcontroladores populares son de 8 bits y dentro de su repertorio incluyen instrucciones para evaluar o modificar bits individuales. Los microprocesadores actuales trabajan con datos de 32 o 64 bits. Sus instrucciones operan directamente sobre palabras de esta magnitud y generalmente no cuentan con instrucciones dedicadas a bits.

Estas notables diferencias entre microprocesadores y microcontroladores los enfocan a diferentes aplicaciones. Un microprocesador generalmente se utiliza como la CPU de una computadora, que es un **Sistema de Propósito General** capaz de realizar cualquier tarea que se le solicite por programación. Su capacidad de procesamiento le posibilita una operación multitarea, es decir, una computadora puede mantener varios procesos en ejecución al mismo tiempo. Los microprocesadores también se pueden encontrar en otros sistemas de procesamiento intensivo como consolas de video juegos o teléfonos inteligentes.

Los microcontroladores están enfocados a **Sistemas de Propósito Específico**, también conocidos como **Sistemas Embebidos**, son sistemas que se crean con una funcionalidad única que no va a cambiar durante su tiempo de vida útil. Por ejemplo: cajas registradoras, hornos de microondas, sistemas de control de tráfico, equipos de sonido, instrumentos musicales, máquinas de escribir, fotocopiadoras, etc.

Las limitaciones de los microcontroladores con respecto a los microprocesadores no son una restricción para este tipo de aplicaciones, si se consideran los siguientes aspectos:

- El tiempo de respuesta en una aplicación de propósito específico no es crítico, las operaciones para monitorear parámetros o actualizar resultados requieren de periodos de tiempo en el orden de milisegundos, periodos que pueden conseguirse con un microcontrolador operando a unos cuantos megahercios.

- Solo realizan una tarea, esto significa que la memoria de código no debe alojar otros programas que nada tengan que ver con la aplicación, como un cargador o un sistema operativo, que son fundamentales en sistemas de propósito general. Por lo tanto, la cantidad de memoria incluida en los microcontroladores llega a ser suficiente. Por otro lado, también hay microcontroladores con diferentes capacidades de memoria de código, que van desde 1 kbyte hasta 256 kbytes, el desarrollador de sistemas puede seleccionar el modelo que mejor se ajuste a sus requerimientos.

Las aplicaciones por lo general utilizan pocas entradas, algunas son directamente de 1 bit y otras pueden ser agrupadas en un puerto de 8 bits, para su procesamiento es suficiente con una CPU que trabaje por bytes. De manera poco frecuente las aplicaciones utilizan datos de 16 bits, por ello, algunos microcontroladores incluyen instrucciones que operan directamente sobre datos de 16 bits, o en caso de ser necesario, puede elegirse un microcontrolador con una CPU de 16 bits. Para las salidas es muy común que se requiera la manipulación directa de 1 bit, el encendido o apagado de un motor, un relevador, una lámpara, etc., no requiere más de 1 bit. Las aplicaciones con salidas analógicas también son realizables porque los microcontroladores pueden generar señales moduladas por ancho de pulso (PWM, pulse width modulation).

Puede observarse que un MCU efectivamente contiene los elementos suficientes para ser considerado como una computadora en un CI, aunque sería una computadora con una capacidad de procesamiento limitada. Los recursos incluidos en un MCU son suficientes para aplicaciones que no demanden un alto rendimiento y que no requieran manejar un conjunto masivo de datos, esto significa que aplicaciones como el procesamiento de video o imágenes, quedan fuera del alcance de un microcontrolador.

#### 1.4. Microcontroladores y FPGAs

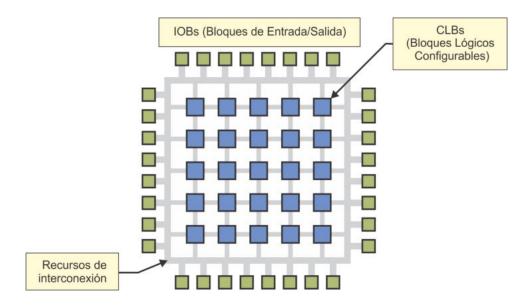

Los FPGAs son dispositivos electrónicos programables que también pueden emplearse como elementos de procesamiento en sistemas electrónicos. La sigla FPGA (Field Programmable Gate Array) hace referencia a un Arreglo de Compuertas Programable en Campo. En la Figura 1.3 se muestra la organización general de un FPGA, en donde puede notarse una disposición matricial de Bloques Lógicos Configurables (CLB, Configurable Logic Block) rodeados por Bloques de Entrada/Salida (IOB, Input/Output Block), además de los recursos necesarios para las conexiones entre CLBs o de CLBs con IOBs.

Los CLBs sirven para programar funciones lógicas combinacionales o secuenciales, con los recursos de interconexión se pueden enlazar diferentes bloques para construir funciones complejas. Dependiendo del fabricante, un CLB va a contener una o más tablas de búsqueda (LUT, look-up table), elementos de estado y hardware para acarreo rápido. La LUT es una pequeña memoria para almacenar una función lógica booleana de 4 o 6 entradas y una salida. Los IOBs proporcionan el mecanismo para que el FPGA se comunique con su entorno, las terminales se configuran por medio de los IOBs como entradas, salidas o bidireccionales.

Los FPGAs se pueden programar con diagramas esquemáticos, utilizando símbolos básicos y conexiones entre ellos. No obstante, por la alta densidad de los dispositivos actuales, es mejor emplear un Lenguaje de Descripción de Hardware (HDL, *Hardware Description Language*). Existen diferentes HDLs, como VHDL, Verilog o ABEL.

Figura 1.3: Organización típica de un FPGA

Un aspecto común entre un FPGA y un MCU es que ambos son dispositivos configurables, con ambos se construyen sistemas flexibles porque la reprogramación del dispositivo modifica el comportamiento del sistema. Pero el programa tiene un objetivo diferente en cada caso, en un FPGA el programa determina qué funciones se van a generar en las LUTs y cómo se van a conectar sus elementos internos, es decir, el programa define al hardware y de esta manera determina el comportamiento de un sistema. En cambio, en un MCU el hardware es fijo y el programa sólo establece el comportamiento de ese hardware.

La organización de los FPGAs hace que el proceso de desarrollo de un sistema sea más complejo y tardado, con respecto al uso de microcontroladores. La ventaja de su uso es que la tecnología actual empleada en su fabricación y el hecho de trabajar directamente en hardware hacen que se alcance una velocidad de procesamiento muy alta (100 MHz o más) en relación a la velocidad de un MCU promedio.

Otra ventaja es que en un FPGA puede hacerse procesamiento concurrente real, si un sistema está organizado en forma modular, los módulos van a revisar sus entradas para generar sus salidas en forma concurrente. En un MCU el procesamiento es secuencial, aunque la inclusión de múltiples recursos facilita la realización simultánea de tareas, en el momento en que un recurso genera un evento que requiere atención de la CPU, la atención se realiza mediante líneas de código secuenciales.

En forma práctica, primero se debería considerar emplear un MCU como el controlador de un sistema electrónico, si se requiere de más velocidad o capacidad de direccionamiento, las alternativas son: un MCU de gama alta o un microprocesador con sus elementos de soporte. Si el sistema va a hacer un procesamiento aritmético intensivo, podría optarse por un procesador digital de señales (DSP, *Digital Signal*

Processor), el cual es un circuito integrado similar a un MCU porque contiene una CPU, memorias y recursos adicionales, la diferencia entre un MCU y un DSP es que el DSP incorpora elementos de hardware enfocados a operaciones aritméticas, como sumadores y multiplicadores, generalmente de punto flotante. Un FPGA es la última opción y es la mejor para aquellos casos en donde se requiere de un hardware especializado, a la medida del sistema, que trabaje a altas velocidades y con módulos concurrentes.

#### 1.5. Organización de los Microcontroladores

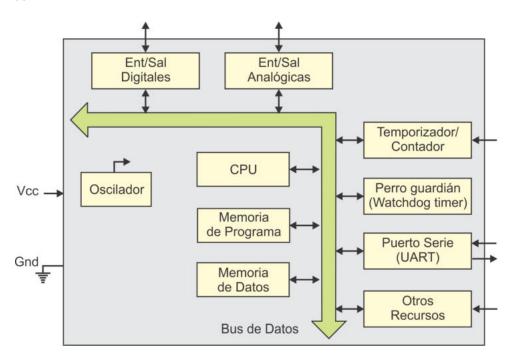

Existe un número grande de fabricantes de microcontroladores y todos manejan diferentes familias con una variedad de modelos, a pesar de ello, hay bloques que son comunes a la mayoría de dispositivos, en la Figura 1.4 se muestra la organización típica de un microcontrolador y en los siguientes apartados se describen sus bloques internos.

Figura 1.4: Organización típica de un microcontrolador

#### 1.5.1. La Unidad Central de Procesamiento (CPU)

La CPU es el bloque principal del microcontrolador, administra todas las actividades que ocurren en el chip y realiza las operaciones sobre los datos, esto mediante la ejecución del programa ubicado en la memoria de código, con ello se determina el comportamiento del sistema controlado por el MCU.

Un programa es una serie de instrucciones combinada de manera lógica para realizar un trabajo específico. Aunque el hardware y el software se complementan, el grado en que un sistema trabaja de manera correcta y eficiente depende muchas veces de la estructura del programa y no de qué tan sofisticada es la CPU.

Para cada instrucción de un programa, el trabajo de la CPU se organiza en tres etapas fundamentales:

- 1. Captura de la Instrucción.

- 2. Decodificación de la misma.

- 3. Ejecución.

Trabajo que realiza a altas velocidades, por lo que el usuario observa el efecto de un programa completo y no de instrucciones individuales.

Cada procesador tiene su propio repertorio de instrucciones. Si un grupo de computadoras o microcontroladores comparten el mismo repertorio pero sus elementos difieren en recursos, costo y rendimiento, entonces este grupo forma una familia de computadoras o de microcontroladores.

Los repertorios de instrucciones difieren entre microcontroladores o microprocesadores, no obstante, existen grupos de instrucciones que son comunes a la mayoría de dispositivos. Estos grupos incluyen instrucciones:

- 1. Aritméticas: suma, resta, producto, división, etc.

- 2. **Lógicas:** AND, OR, XOR, NOT, etc.

- 3. Transferencias de datos: directas o indirectas.

- 4. **Bifurcaciones o saltos:** condicionales o incondicionales.

Una computadora es un sistema originalmente planeado para procesamiento de datos, por lo que podría pensarse que las instrucciones de mayor uso son aritméticas o lógicas, sin embargo, actualmente las computadoras han ampliado tanto su campo de acción que las aplicaciones comunes hacen un uso exhaustivo de transferencias de datos. El ejemplo típico es el procesador de palabras, el programa transfiere datos del espacio disponible para entradas y salidas, a memoria principal y a memoria de video, cuando se respalda un documento, la información es transferida de memoria principal a memoria secundaria, puede notarse que básicamente son transferencias de datos con un nulo procesamiento aritmético o lógico.

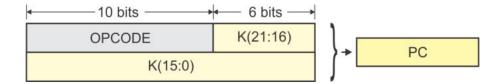

Una instrucción es una cadena de 1's y 0's que la computadora reconoce e interpreta, en esa cadena existen diferentes grupos de bits que se conocen como campos de la instrucción. El **código de operación** u **opcode** es un campo presente en todas las instrucciones porque determina la operación a realizar. Las instrucciones también

deben incluir campos para los operandos, estos indican la ubicación de los datos a los que se aplica la operación.

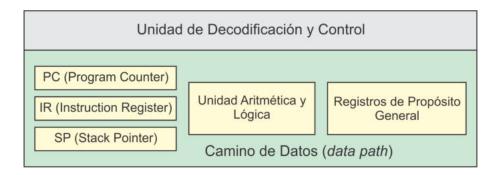

Figura 1.5: Elementos comunes en una CPU

#### Organización de una CPU

A pesar de que existe una diversidad de fabricantes de procesadores, hay elementos que son comunes a todos ellos. En la Figura 1.5 se muestran los bloques típicos de una CPU, los cuales se pueden clasificar en dos grupos: el Camino de Datos y la Unidad de Decodificación y Control. El Camino de Datos involucra los elementos por donde va a fluir la información cuando se ejecute una instrucción y la Unidad de Decodificación y Control determina qué elementos se activan dentro del Camino de Datos para la correcta ejecución de cada instrucción.

Como parte del camino de datos, en la Figura 1.5 se observan tres registros con una función específica:

- El Contador de Programa (PC, *Program Counter*) contiene la dirección de la instrucción que se va a ejecutar en un instante de tiempo determinado y mientras esa instrucción se ejecuta, el **PC** automáticamente actualiza su valor para apuntar a la siguiente instrucción a ejecutar.

- El **Registro de Instrucción** (IR, *Instruction Register*) contiene la cadena de bits que conforman a la instrucción bajo ejecución, de esa cadena, la unidad de control analiza al campo del opcode para determinar la activación de las señales en los demás elementos en la CPU.

- El **Apuntador** de **Pila** (SP, *Stack Pointer*) contiene la dirección del tope de la pila, que es un espacio de almacenamiento utilizado durante la invocación de rutinas. La llamada a una rutina requiere que el valor del **PC** sea respaldado en la pila, con ello, el **SP** se ajusta automáticamente al nuevo tope. Cuando la rutina termina se extrae el valor del tope de la pila y se remplaza al **PC**, para que el programa continúe con la instrucción posterior al llamado de la rutina, esto también requiere un ajuste del **SP**.

Además de las llamadas a rutinas algunos procesadores incluyen instrucciones para hacer respaldos (push) y recuperaciones (pop) en forma explícita. Instrucciones que también producen cambios automáticos en el SP.

Los registros de propósito general son los elementos más rápidos para el almacenamiento de variables. Dado que el número de registros en una CPU es limitado, si no es suficiente para todas las variables requeridas por un programa, debe utilizarse la memoria de datos para su almacenamiento.

La Unidad Aritmética y Lógica es el bloque que se encarga de realizar las operaciones aritméticas y lógicas con los datos guardados en los registros de propósito general, no obstante, en ocasiones también opera sobre direcciones para calcular el destino de un salto o la ubicación de una localidad a la que se va a tener acceso para una transferencia de memoria a registro o viceversa.

#### Tareas de la CPU

Con cada instrucción la CPU realiza tres tareas fundamentales: Captura, Decodificación y Ejecución.

La Captura de una Instrucción es una tarea que involucra los siguientes pasos:

- 1. El contenido del PC se coloca en el bus de direcciones.

- 2. La CPU genera una señal de control para habilitar la lectura de memoria de código.

- 3. Una instrucción se obtiene de la memoria de código y se coloca en el IR.

- 4. El PC es preparado para la siguiente instrucción.

Una vez que la instrucción está en el **IR** el procesador continúa con su decodificación. Decodificar consiste en descifrar el opcode para generar las señales de control adecuadas para el tipo de instrucción.

Finalmente, la tercer tarea de la CPU es la Ejecución. Ejecutar una instrucción puede involucrar: habilitar a la ALU para que genere algún resultado, cargar un dato de memoria y llevarlo a un registro, almacenar el contenido de un registro en memoria o modificar el valor del **PC** para un salto. La unidad de decodificación y control genera las señales requeridas por cada instrucción.

#### Tipos de CPU

De acuerdo con su organización interna una CPU puede ser CISC o RISC. Con CISC se hace referencia a computadoras con un Repertorio de Instrucciones Complejo (CISC, Complex Instruccion Set Computers) y RISC es para referir a computadoras con un Repertorio de Instrucciones Reducido (RISC, Reduced Instruccion Set Computers).

En el diseño de las primeras computadoras se buscó que el programador escribiera programas compactos, para ello, las instrucciones deben realizar tareas complejas y, por lo tanto, requieren de un hardware extenso para su ejecución. Esto afecta el rendimiento de las computadoras porque significa que el ciclo de reloj debe ser largo o que se van a necesitar varios ciclos de reloj para la ejecución de cada instrucción. La complejidad en el hardware para ejecutar este tipo de instrucciones hace que estas computadoras correspondan a la categoría CISC.

La filosofía **RISC** es opuesta, para aumentar el rendimiento los diseños se orientaron a instrucciones con tareas muy simples, esto hace posible que el hardware trabaje a frecuencias mucho más grandes.

Una arquitectura **RISC** tiene pocas instrucciones y generalmente son del mismo tamaño; en una arquitectura **CISC** hay demasiadas instrucciones con diferentes tamaños y formatos, que pueden ocupar varios bytes, uno para el opcode y los demás para los operandos.

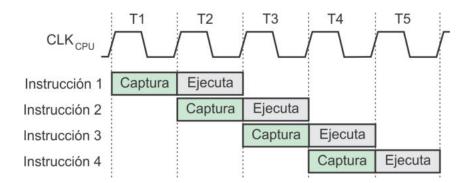

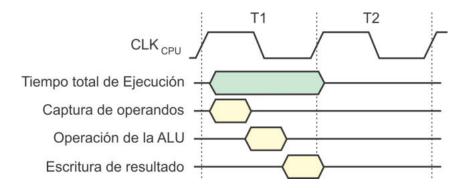

La tarea realizada por una instrucción **CISC** generalmente requiere de varias instrucciones **RISC**, sin embargo, la simplicidad en las tareas de las instrucciones **RISC** permite que en la organización del procesador se apliquen técnicas como la segmentación<sup>2</sup>, que consiste en el traslape de diferentes instrucciones en cada una de las etapas del procesador, por ejemplo, mientras una instrucción se está ejecutando, otra puede estar en proceso de decodificación y la siguiente en la etapa de captura. El número de instrucciones que simultáneamente están en el procesador depende del número de etapas de segmentación incluidas.

Además, el hardware de un procesador **RISC** es tan simple que actualmente es frecuente encontrar varios núcleos en un circuito integrado.

Es por ello que desde los 90's prácticamente todos los nuevos procesadores son **RISC** y los que originalmente fueron **CISC** se han convertido en un híbrido que acepta instrucciones complejas e internamente las separa en microinstrucciones o instrucciones simples para ser procesadas en flujos de ejecución del tipo **RISC**.

#### 1.5.2. Sistema de Memoria

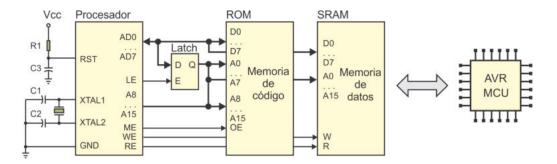

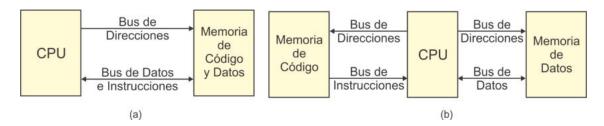

Una computadora (y por lo tanto, también un microcontrolador) debe contar con espacios de memoria para almacenar los programas (código) y los datos. En relación a cómo se organizan estos espacios se tienen dos modelos de computadoras, un modelo en donde el código y datos comparten el mismo espacio de memoria y el otro en donde se tienen memorias separadas, una para código y otra para datos, estos se ilustran en la Figura 1.6.

$<sup>^2\</sup>mathrm{La}$  segmentación proporciona un paralelismo al nivel de instrucciones que queda transparente al programador.

Figura 1.6: Modelos de computadoras respecto a la organización de la memoria (a) Arquitectura von Neumann y (b) Arquitectura Harvard

John von Neumann<sup>3</sup> propuso el concepto de programa almacenado, el cual establece que las instrucciones se lleven a memoria como si fueran datos, para que posteriormente se ejecuten sin tener que escribirlas nuevamente, por lo tanto, se requiere de un solo espacio de memoria para almacenar instrucciones y datos. Este concepto fue primeramente aplicado en la Computadora Automática Electrónica de Variable Discreta (EDVAC, *Electronic Discrete-Variable Automátic Computer*), desarrollada por Von Neumann, Eckert y Mauchly. Actualmente ha sido adoptado por los diseñadores de computadoras porque proporciona flexibilidad a los sistemas. Si una computadora se basa en este concepto, se dice que tiene una Arquitectura tipo von Neumann.

Mientras la tendencia natural para los diseñadores de computadoras fue adoptar el concepto de programa almacenado, en la Universidad de Harvard desarrollaron la Mark I, la cual almacenaba instrucciones y datos en cintas perforadas, pero incluía interruptores rotatorios de 10 posiciones para el manejo de registros. Actualmente, si una computadora tiene un espacio para el almacenamiento de código físicamente separado del espacio para los datos, se dice que tiene una Arquitectura Harvard.

La mayoría de microcontroladores utilizan una Arquitectura Harvard. En la memoria de código se alojan las instrucciones que conforman el programa y algunas constantes. Algunos microcontroladores, además de su memoria interna, tienen la capacidad de direccionar memoria externa de código para soportar programas con una cantidad grande de instrucciones.

La memoria de programa generalmente es no volátil y puede ser del tipo EPROM, EEPROM, Flash, programable una sola vez (OTP, one-time programmable) o ROM enmascarable. Los primeros 3 tipos son adecuados durante las etapas de prototipado, la memoria OTP es conveniente si se va a hacer una producción de pocas unidades de un sistema y la ROM enmascarable es la más acertada para una producción masiva.

<sup>&</sup>lt;sup>3</sup>John von Neumann, (28 de diciembre de 1903 - 8 de febrero de 1957) Matemático húngaroestadounidense, doctorado por la Universidad de Budapest a los 23 años. Realizó contribuciones importantes en física cuántica, análisis funcional, teoría de conjuntos, informática, economía, análisis numérico, estadística y muchos otros campos.

Con respecto a la memoria de datos, los microcontroladores contienen un espacio de SRAM y algunos también incluyen EEPROM. La SRAM se utiliza para el almacenamiento de variables y el manejo de una pila para organizar las llamadas a rutinas. La EEPROM sirve para almacenar aquellos datos que se deben conservar aun en ausencia de energía. Todos los microcontroladores tienen una SRAM interna de diferentes magnitudes, algunos además cuentan con la capacidad de expansión por medio de una memoria externa.

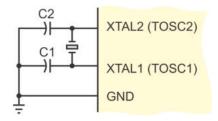

#### 1.5.3. Oscilador

La CPU va tomando las instrucciones de la memoria de programa para su posterior ejecución a cierta frecuencia. Esta frecuencia está determinada por el circuito de oscilación, el cual genera la frecuencia de trabajo a partir de elementos externos como un circuito RC, un resonador cerámico o un cristal de cuarzo, aunque algunos microcontroladores incluyen un oscilador RC calibrado interno para reducir el tamaño del sistema final. Tan pronto como se suministra la alimentación eléctrica a un MCU, el oscilador empieza con su operación.

#### 1.5.4. Temporizador/Contador

El Temporizador/Contador (timer/counter) es un recurso con una doble función, como temporizador se utiliza para coordinar acciones periódicas y como contador sirve para que una tarea se realice cuando ocurre una cantidad predeterminada de eventos externos.

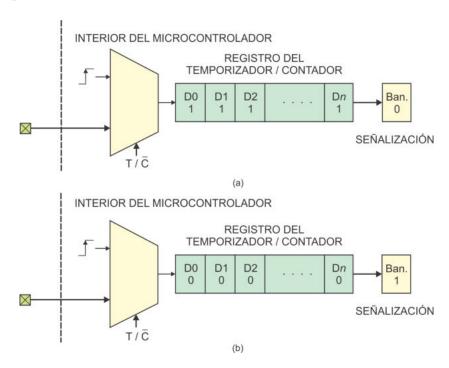

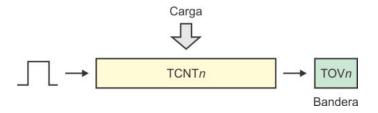

Se compone de un registro de n-bits que se incrementa en cada ciclo de reloj o cuando ocurre un evento externo, según el modo de operación. Cuando el registro desborda se genera una señalización, es decir, se pone en alto una bandera para indicar a la CPU que ha pasado un intervalo de tiempo o que ha ocurrido un número esperado de eventos. El desbordamiento ocurre cuando el registro alcanza su valor máximo (todos los bits del registro en 1) y la cuenta se reinicia (todos los bits en 0). La organización básica de un temporizador se muestra en la Figura 1.7.

El registro del temporizador tiene un comportamiento ascendente y puede ser precargado para reducir el número de eventos a contar. Mientras el temporizador trabaja, la CPU puede emplear su tiempo de procesamiento en otras tareas, dentro de las cuales debe reservar un espacio para monitorear la bandera, o bien, configurar al recurso para que genere una interrupción.

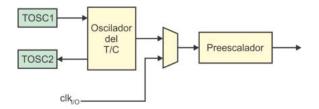

En algunos microcontroladores, la entrada del temporizador es precedida por un preescalador, el cual básicamente es un divisor de frecuencia configurable con el que se puede contar un número más grande de eventos y, por lo tanto, alcanzar intervalos de tiempo mayores.

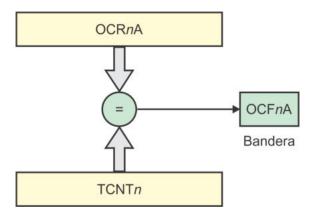

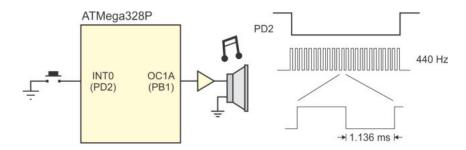

Los temporizadores en los MCUs modernos tienen funciones adicionales, incluyen

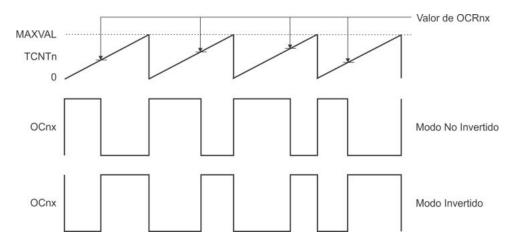

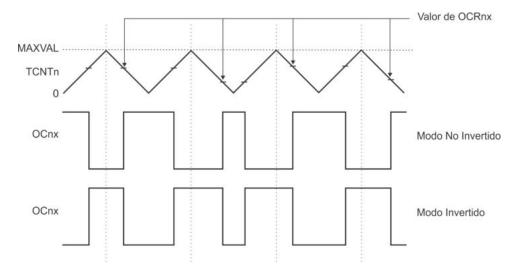

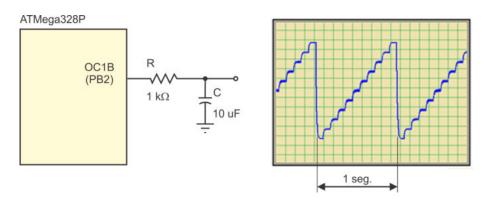

registros de comparación para que ante coincidencias con el temporizador se puedan producir respuestas automáticas en algunas de sus terminales, de esta forma se pueden generar tonos a determinadas frecuencias o señales moduladas en ancho de pulso (PWM, pulse width modulation). PWM es una técnica para manipular dispositivos analógicos desde salidas digitales, al modificar el ciclo de trabajo de una señal periódica.

Figura 1.7: Organización básica de un Temporizador/Contador, en (a) el registro ha alcanzado su valor máximo y en (b) al reiniciar la cuenta se genera una señalización

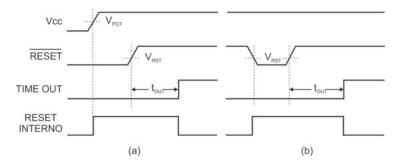

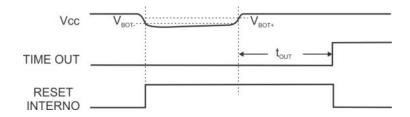

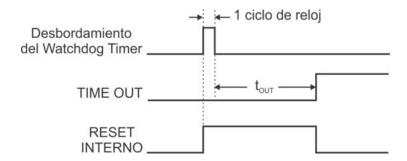

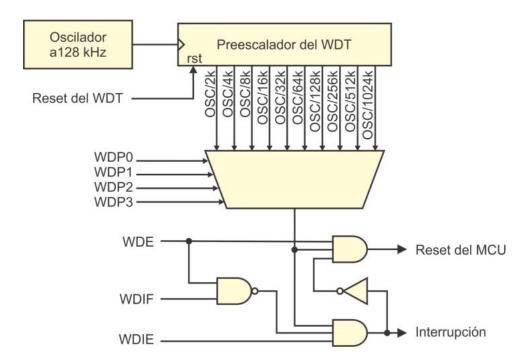

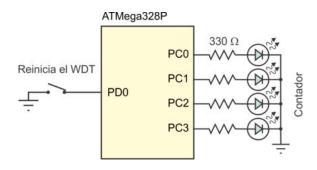

#### 1.5.5. Perro Guardián (WDT, watchdog timer)

El WDT (watchdog timer) también es un temporizador y, por lo tanto, también se compone de un registro de n-bits, solo que cuando desborda ocasiona un reinicio del sistema (reset). El objetivo del WDT es evitar que el microcontrolador se cicle en estados no contemplados, lo cual llega a ser muy útil en sistemas autónomos, el microcontrolador se puede ciclar ante situaciones inesperadas, como variaciones en la fuente de alimentación o por la desconexión repentina de un periférico.

En algunos microcontroladores el WDT se debe activar en el momento en que se programa al dispositivo, otros permiten activarlo o desactivarlo dentro del programa de aplicación, siempre que se siga alguna secuencia de seguridad para evitar activaciones no deseadas. En cualquier caso, si se utiliza al WDT, en posiciones estratégicas del programa principal deben incluirse instrucciones para su reinicio y con ello se evita su desbordamiento.

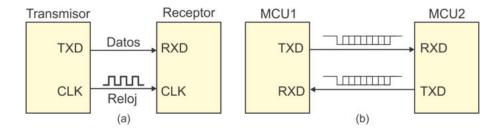

Figura 1.8: Comunicación serial (a) síncrona y (b) asíncrona

#### 1.5.6. Puerto Serie

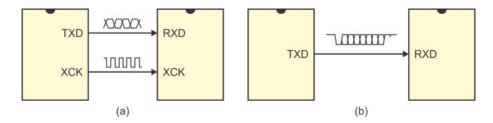

La mayoría de microcontroladores cuentan con un receptor/transmisor universal asíncrono (UART, *Universal Asynchronous Receiver and Transmitter*), para una comunicación serial con dispositivos o sistemas externos, bajo protocolos y razones de transmisiones estándares. La comunicación serial puede ser de dos tipos:

- Síncrona: Además de la línea de datos se utiliza una línea para la señal de reloj.

- **Asíncrona:** Solo hay líneas para los datos, la comunicación se realiza con éxito si el transmisor y el receptor se configuran con la misma velocidad de transferencia (bits/segundo, *Baud Rate*) y el mismo formato para los datos.

La comunicación serial es muy útil porque solo requiere de un alambre o línea de conexión y tiene un alcance mucho mayor que una transmisión paralela (de varios bits). El hardware para la comunicación serial básicamente consiste en una conversión de paralelo a serie para el transmisor o de serie a paralelo para la recepción. Puede realizarse entre un microcontrolador con una computadora, entre microcontroladores o un microcontrolador con otros sistemas que incluyan un puerto de comunicación serial. En la Figura 1.8 se ilustra la diferencia entre la comunicación síncrona y asíncrona.

#### 1.5.7. Entradas y Salidas Digitales

Los microcontroladores incluyen puertos digitales que funcionan como entradas o salidas para intercambiar datos con el exterior. A diferencia de un puerto serie, en donde se transfiere un bit a la vez, en los puertos digitales es posible realizar un intercambio de bytes.

Todos los microcontroladores tienen puertos digitales, aunque el número de puertos o el número de bits por puerto pueden variar entre dispositivos. Como entradas se utilizan para el monitoreo de dispositivos digitales como botones, interruptores, teclados, sensores con salida a relevador, etc., y como salidas sirven para el manejo de LEDs, displays de 7 segmentos, activación de motores, LCD, etc.

#### 1.5.8. Entradas y Salidas Analógicas

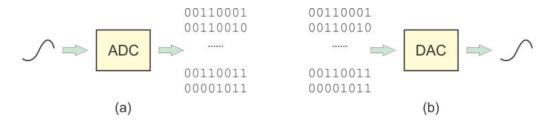

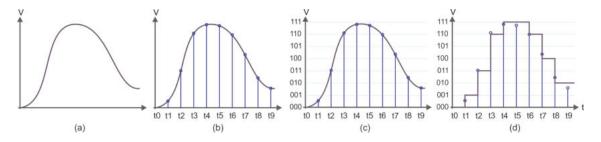

Para entradas, algunos microcontroladores incorporan un convertidor analógico a digital (ADC, *Analogic-Digital Converter*) o un comparador analógico, ambos son muy útiles porque sin elementos externos es posible monitorear parámetros analógicos como temperatura, velocidad, humedad, etc.

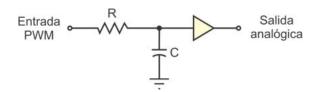

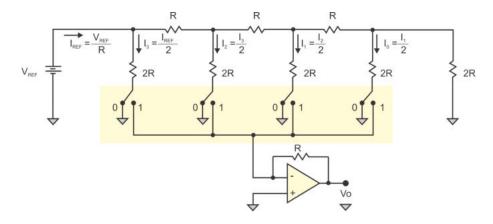

Para salidas, podría considerarse el uso de un convertidor digital a analógico (DAC, Digital-Analogic Converter) pero no es común que un microcontrolador contenga un DAC, en lugar de ello, los microcontroladores incluyen salidas PWM para manejar cargas analógicas desde terminales digitales, sin elementos externos se puede manipular la intesidad de unos LEDs o la velocidad de un motor.

#### 1.6. Clasificación de los Microcontroladores

Existen diferentes formas de clasificar a los microcontroladores y no son excluyentes unas de otras. En esta sección se describen las formas típicas de clasificación.

Por la arquitectura de la CPU, los microcontroladores pueden ser **RISC**, si el dispositivo tiene un hardware simple o **CISC** si sus instrucciones requieren de un hardware complejo para su ejecución. Prácticamente los nuevos microcontroladores son **RISC**.

Con respecto al tamaño de los datos, se tienen microcontroladores de 8, 16 y hasta 32 bits. Por el tamaño de los datos debe entenderse el tamaño de los registros de trabajo y por lo tanto, corresponde con el número de bits de los operandos en la ALU, este parámetro generalmente difiere del tamaño de las instrucciones, el cual no es empleado para una clasificación.

Tomando como base la organización y el acceso a la memoria de código y datos, se tienen 2 modelos: Arquitectura von Neumann y Arquitectura Harvard.

Considerando la memoria y sus capacidades de expansión, cuando un microcontrolador está acondicionado para tener acceso a memoria externa, se dice que tiene una **arquitectura abierta**, en caso contrario su **arquitectura es cerrada**. Con una arquitectura abierta, además de manejar memoria externa, es posible el manejo de periféricos externos mapeándolos en el espacio de la memoria de datos, es decir, algunas direcciones hacen referencia a un periférico y no a datos de la memoria.

La última clasificación tiene que ver con la forma en que los datos son almacenados y manipulados por la CPU. En este esquema se distingue a las arquitecturas de acuerdo a cómo la ALU tiene acceso a los operandos involucrados en una instrucción aritmética o lógica. Bajo este criterio se distinguen cuatro tipos de arquitectura: Pila, Acumulador, Registro-Memoria y Registro-Registro.

En una arquitectura tipo Pila, como su nombre lo indica, los datos deben ingresar

a una pila para ser procesados, las operaciones se realizan con los últimos datos ingresados y el resultado se deja en el tope de la misma. Por ejemplo, para realizar la operación de alto nivel:

$$A = B - C$$

suponiendo que A, B y C son variables almacenadas en memoria, se tiene la secuencia de instrucciones:

```

PUSH B ; La variable B ingresa en la pila

PUSH C ; La variable C ingresa en la pila

SUB ; La resta se hace con los datos de la pila

POP A ; Extrae el resultado y lo almacena en A

```

Una arquitectura tipo **Acumulador** basa su operación en un registro con el mismo nombre. El Acumulador es el registro de trabajo por lo que debe ser uno de los operandos de la ALU y el resultado también queda en el acumulador. Las instrucciones que únicamente requieren de un operando se aplican sobre el acumulador.

Si la misma operación de resta se realiza en una arquitectura tipo acumulador, las instrucciones resultantes son las siguientes (Acc representa al acumulador):

```

MOV Acc, B ; Transfiere la variable B al Acumulador

SUB Acc, C ; Resta C de Acc (en Acc queda el resultado)

MOV A, Acc ; Transfiere el Acumulador a la variable A

```

En una arquitectura del tipo **Registro-Memoria** el procesador está acondicionado para que uno de los operandos de la ALU esté en memoria mientras el otro debe estar en uno de los registros de propósito general. La operación bajo consideración se realiza con las siguientes instrucciones:

```

LD R1, B ; Carga la variable B en el registro R1

SUB R1, C ; Resta la variable C de R1

ST A, R1 ; Almacena R1 en la variable A (en memoria)

```

Finalmente, en una arquitectura del tipo **Registro-Registro** los dos operandos que llegan a la ALU deben estar en registros de propósito general. Las arquitecturas de este estilo también son conocidas como Arquitecturas tipo Carga-Almacenamiento, esto porque cuando se van a operar variables que están en memoria primero deben ser cargadas en registros, el resultado queda en un registro y, por lo tanto, se requiere de un almacenamiento para llevarlo a una variable de memoria. Para el mismo ejemplo se tienen las instrucciones siguientes:

```

LD R1, B ; Carga la variable B en R1

LD R2, C ; Carga la variable C en R2

SUB R1, R2 ; La ALU opera con los registros R1 y R2

ST A, R1 ; Almacena el resultado en la variable A

```

Este libro está enfocado al microcontrolador **ATMega328P**, un microcontrolador **RISC** de 8 bits, con una Arquitectura **Harvard** que es **cerrada** y sus operaciones son del tipo **Registro-Registro**.

#### 1.7. La Tarjeta Arduino

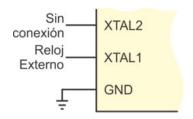

La tarjeta Arduino es una plataforma electrónica originalmente enfocada a personas con poca experiencia en programación y conocimientos básicos de electrónica, el objetivo de sus creadores fue dotar de herramientas tecnológicas a diseñadores y artistas para complementar sus invenciones, sin embargo, al rededor de Arduino se fue creando una comunidad de desarrolladores que creció sustancialmente y actualmente en el mercado existe una cantidad enorme de tarjetas de desarrollo y módulos para expandir sus capacidades. Este aspecto resultó muy atractivo para los desarrolladores de sistemas basados en microcontroladores, porque con Arduino se simplificó la evaluación de sensores, actuadores o interfaces de comunicación.

Con Arduino se involucran tres elementos principales:

- El IDE o entorno en el que se desarrollan los programas, el IDE incluye un lenguaje de programación de código abierto soportado por un gran número de bibliotecas de funciones enfocadas al manejo de recursos internos y periféricos externos, con ejemplos de cómo utilizarlos.

- Las tarjetas de desarrollo, que varían en precio y características, pero que están soportadas por microcontroladores AVR de Microchip. Por ejemplo, el ATMega328P es empleado en los modelos Arduino UNO, Arduino Mini y Arduino LilyPad, entre otros. Una tarjeta con mayores prestaciones es la Arduino Mega, manejada por un ATMega2560. Los diagramas de las tarjeras Arduino son públicos bajo una licencia de Creative Commons.

- El tercer elemento son los módulos de expansión, referidos como *shields*. Lo interesante de los *shields* es que la comunidad de Arduino no solo ha diseñado el hardware, también ha desarrollado las bibliotecas de funciones que pueden integrarse al IDE para su evaluación rápida.

Al emplear tarjetas Arduino ya se está trabajando con microcontroladores, sin embargo, las ventajas para el desarrollo rápido de sistemas a través del entorno dejan un vacío de conocimientos sobre estos dispositivos, lo que complica la optimización de los sistemas que se puede conseguir con un manejo directo de los registros.

Por ello, Arduino es una excelente opción para iniciar con el uso de microcontroladores, después de las primeras experiencias es conveniente entender su organización para estar en condiciones de desarrollar bibliotecas de funciones propias, así como la posibilidad de crear un hardware a la medida de las especificaciones de un sistema. El hardware y software deben adecuarse a los requerimientos de un sistema y no debe ocurrir que los sistemas se restrinjan por las características de una tarjeta de desarrollo.

La flexibilidad de Arduino permite expandir el entorno agregando bibliotecas de C/C++. También es posible incorporar código AVR-C directamente en los *sketchs* o programas de Arduino, en algunos de los ejemplos descritos en el texto se hace

este ejercicio, sobre todo en donde el código C simplifica un *sketch* en contraste a emplear únicamente código Arduino.

#### 1.8. Sistemas Embebidos e Internet de las Cosas

Los **sistemas embebidos** o empotrados son sistemas de propósito específico basados en microcontroladores, FPGAs o tarjetas de desarrollo como Arduino, la característica principal es que el usuario no detecta la presencia del dispositivo programable y solo aprovecha sus beneficios.

El avance en la tecnología ha llevado a una miniaturización en los componententes electrónicos, lo que permite empotrar sistemas completos de procesamiento en artículos electrónicos convencionales o subsistemas electrónicos que son parte de un sistema complejo, el nombre de **Sistema Embebido** surgió de manera natural con esta integración. Un sistema embebido cumple con la funcionalidad original para la cual fue creado pero está dotado de la inteligencia que le proporciona el procesador empotrado, el cual también le da un soporte para ampliar sus capacidades.

Los microcontroladores son la base para los sistemas embebidos, también se llegan a emplear FPGAs, aunque es menos frecuente. El MCU es un control computarizado dentro del sistema, al cual le brinda inteligencia y le agrega un valor substancial al producto final. A pesar de su extenso uso, la mayoría de personas no es consciente de que tiene un contacto continuo con varios sistemas embebidos, en el auto, el hogar y la oficina.

Por ejemplo, una cafetera es un electrodoméstico simple que calienta el agua de un depósito por medio de una resistencia eléctrica, el agua se bombea automáticamente cuando alcanza su punto de ebullición y de esta manera llega al compartimiento del café, el usuario determina el encendido y apagado de la cafetera. La cafetera se convierte en un sistema embebido si un microcontrolador interno maneja un reloj de tiempo real y a través de periféricos como un display y botones, le permite al usuario configurar tareas como el encendido a una hora predeterminada, el apagado después de un tiempo de operación o el apagado urgente en caso de detectar un exceso de corriente debido a alguna falla, entre otras posibles funciones.

Por otra parte, la frase Internet de las Cosas (IoT, Internet of Things) indica que actualmente no solo las computadoras se pueden conectar a Internet, sino que también algunos sistemas embebidos cuentan con esta conexión, ya sea por cable o de manera inalámbrica. Un sistema embebido se convierte en un dispositivo del Internet de las cosas cuando puede ser monitoreado o manipulado a distancia, no todos los sistemas embebidos tienen esta propiedad, en algunos casos resulta innecesario. Para el ejemplo de la cafetera, esta sería un dispositivo IoT si desde una página web se pudiera monitorear su estado o realizar su encendido o apagado.

El Internet de las Cosas es algo mucho más amplio que dotar de conexiones a los

32 1.9. EJERCICIOS

sistemas embebidos, también involucra el manejo de protocolos de red, gestión y almacenamiento de datos, seguridad e interfaces. Esto hace necesario el uso de microcontroladores de gama alta para el desarrollo de sistemas IoT, un ATMega328P queda limitado para ello, a menos que se complemente con módulos que apoyen esa funcionalidad.

#### 1.9. Ejercicios

- 1. ¿Qué es un microcontrolador?

- 2. Describa qué es un sistema embebido y por qué es conveniente el uso de microcontroladores en sistemas embebidos.

- 3. Exprese las diferencias entre microcontroladores y microprocesadores, considere sus características de hardware y aplicaciones.

- 4. Explique en qué situaciones es conveniente o necesario el uso de un FPGA en lugar de un MCU.

- 5. Realice un diagrama con la organización típica de un microcontrolador.

- 6. Describa el papel de una CPU en un microcontrolador (o computadora) y explique las tareas que realiza con cada instrucción.

- 7. Indique el objetivo de los registros de propósito específico comúnmente encontrados en una CPU:

- a) Program Counter (PC)

- b) Instruction Register (IR)

- c) Stack Pointer (SP)

- 8. Liste los grupos de instrucciones típicos que maneja una CPU.

- 9. Explique en qué difiere una arquitectura Harvard de una arquitectura basada en el modelo de von Neumann.

- 10. Explique las diferencias entre una arquitectura RISC y una arquitectura CISC.

- 11. Indique los tipos de memoria utilizados por los microcontroladores para el almacenamiento de instrucciones y para el almacenamiento de datos.

- 12. Explique la función de los siguientes recursos en un microcontrolador:

- a) Oscilador Interno

- b) Temporizador (timer)

- c) Perro guardián (watchdog timer)

- d) Puerto Serie

- e) Entradas y salidas digitales

- f) Entradas y salidas analógicas

- 13. Para la operación en alto nivel A=B+C+D, suponiendo que A, B, C y D son variables ubicadas en memoria de datos, muestre cómo se traduce a ensamblador para una arquitectura:

- a) Tipo Pila

- b) Tipo Acumulador

- c) Tipo Registro-Memoria

- d) Tipo Registro-Registro (Carga-Almacenamiento)

Utilice la instrucción ADD para la suma.

# Capítulo 2

# Los Microcontroladores AVR

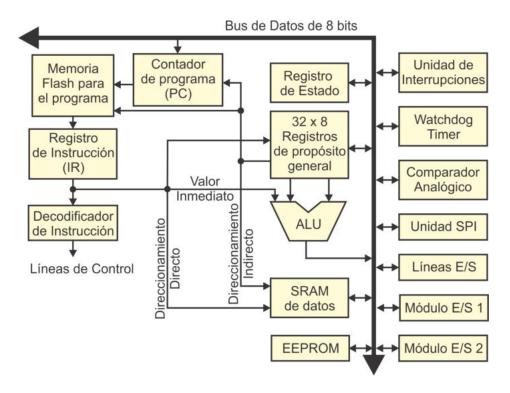

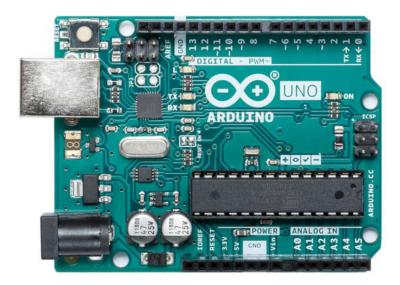

Los microcontroladores AVR incluyen un procesador RISC de 8 bits, su arquitectura es del tipo Harvard y sus operaciones se realizan bajo un esquema Registro-Registro.

Este capítulo hace referencia al hardware de los microcontroladores AVR, específicamente del ATMega328P, se describe su organización interna y sus características de funcionamiento.

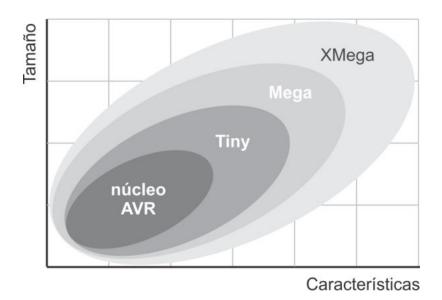

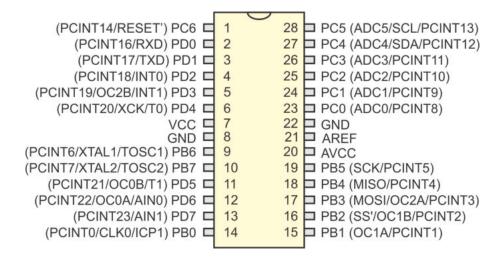

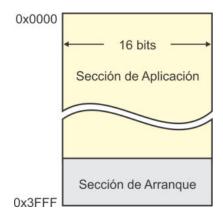

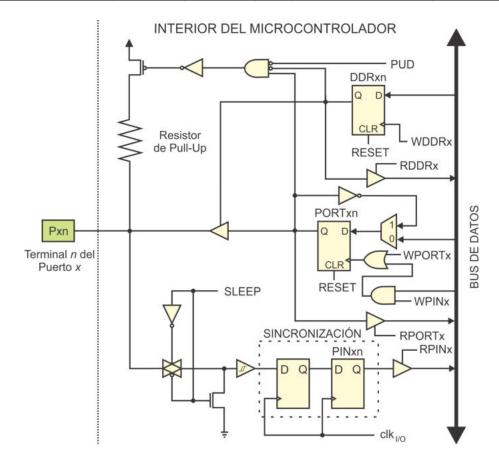

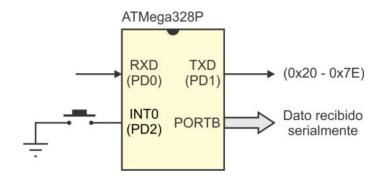

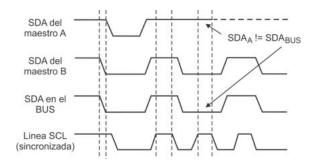

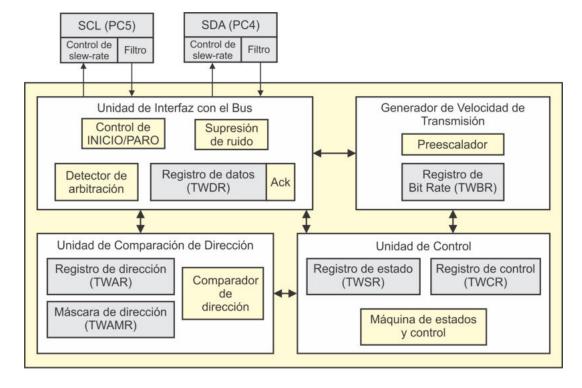

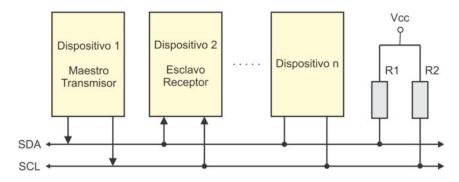

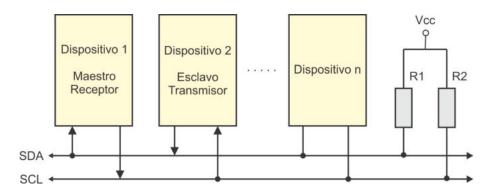

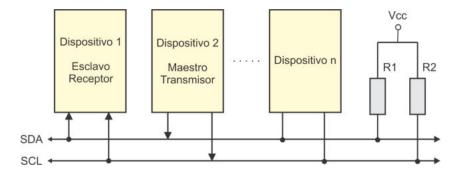

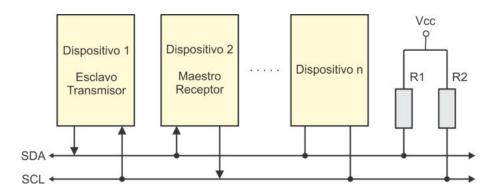

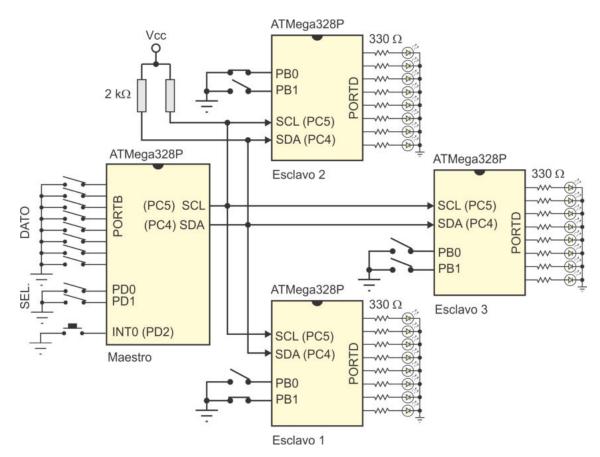

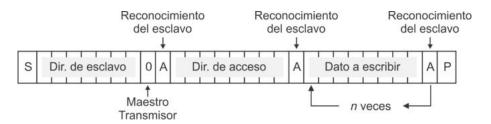

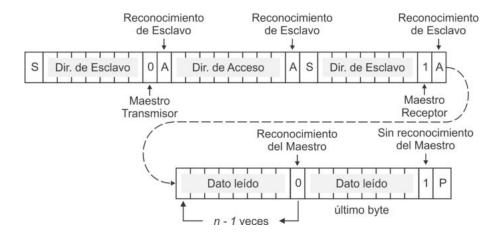

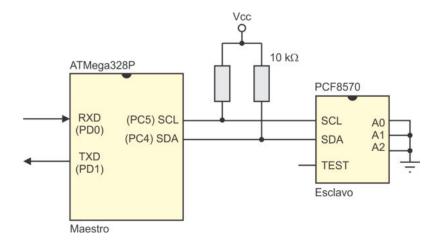

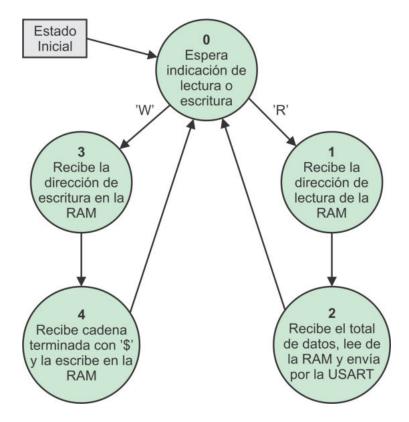

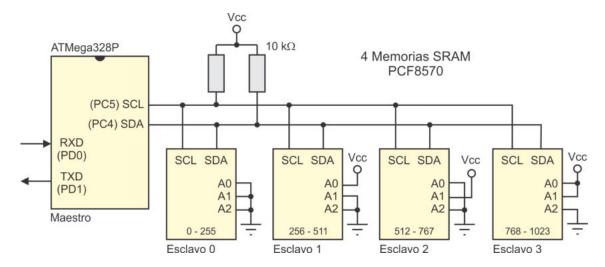

### 2.1. Características Generales